Integrated circuits

Book IC10

1986

Memories MOS, TTL, ECL **Elcoma** – Philips Electronic Components and Materials Division – embraces a world-wide group of companies operating under the following names:

Miniwatt Signetics

Mullard

PHILIPS

Elcoma offers you a technological partnership in developing your systems to the full. A partnership to which we can bring

- world-wide production and marketing

- know-how

- systems approach

- continuity

- broad product line

- fundamental research

- leading technologies

- applications support

- quality

## MEMORIES MOS, TTL, ECL

|                              | page |

|------------------------------|------|

| Selection guide              |      |

| Functional index             |      |

| Numerical index              | 5    |

| MOS Memories                 |      |

| Introduction                 |      |

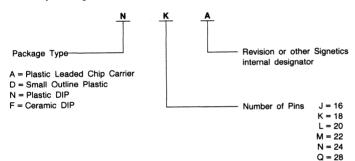

| Type designation             | 13   |

| Rating systems               |      |

| Handling MOS devices         |      |

| CMOS RAM                     | 15   |

| CMOS EEPROM                  | 111  |

| Charge-Coupled Memory        | 121  |

| <i>C</i>                     |      |

| TTL Memories                 | 131  |

| Introduction                 |      |

| Quality and Reliability      |      |

| Selection Guide              |      |

| PROM Cross Reference Guide   |      |

| RAM Cross Reference Guide.   | 14/  |

| Ordering Information         | 1.44 |

| 64-bit RAM                   | 145  |

| 256-bit RAM                  |      |

| Byte-Organized RAM           |      |

| PROM Programming Information | 106  |

| Low Complexity PROM          | 100  |

| 4K-bit PROM                  | 225  |

| 8K-bit PROM                  | 241  |

| 16K-bit PROM                 |      |

| 32K-bit PROM                 |      |

| 64K-bit PROM                 |      |

| OHR-UILT KOM                 |      |

| ECL Memories.                | 207  |

| ECL RAM                      | 200  |

|                              |      |

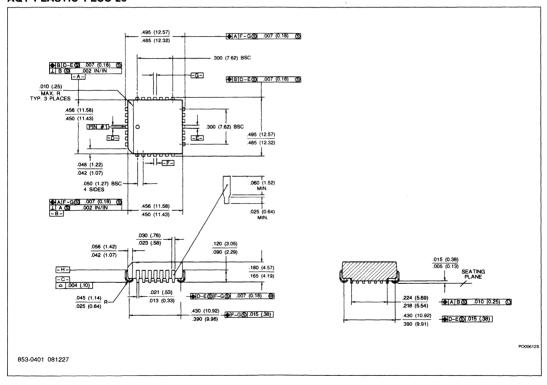

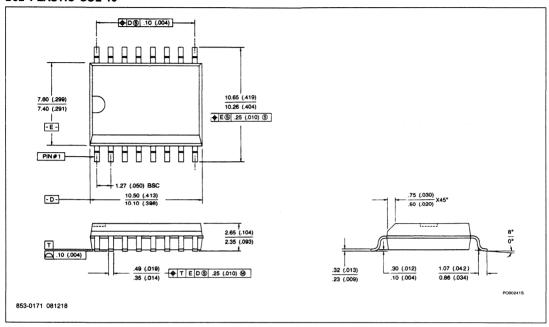

| Package information          |      |

## DATA HANDBOOK SYSTEM

Our Data Handbook System comprises more than 60 books with specifications on electronic components, subassemblies and materials. It is made up of four series of handbooks:

**ELECTRON TUBES**

BLUE

**SEMICONDUCTORS**

RED

INTEGRATED CIRCUITS

**PURPLE**

COMPONENTS AND MATERIALS

**GREEN**

The contents of each series are listed on pages iv to viii.

The data handbooks contain all pertinent data available at the time of publication, and each is revised and reissued periodically.

When ratings or specifications differ from those published in the preceding edition they are indicated with arrows in the page margin. Where application information is given it is advisory and does not form part of the product specification.

Condensed data on the preferred products of Philips Electronic Components and Materials Division is given in our Preferred Type Range catalogue (issued annually).

Information on current Data Handbooks and on how to obtain a subscription for future issues is available from any of the Organizations listed on the back cover.

Product specialists are at your service and enquiries will be answered promptly.

## ELECTRON TUBES (BLUE SERIES)

The blue series of data handbooks comprises:

| T1   | Tubes for r.f. heating                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------|

| T2a  | Transmitting tubes for communications, glass types                                                                             |

| T2b  | Transmitting tubes for communications, ceramic types                                                                           |

| Т3   | Klystrons                                                                                                                      |

| T4   | Magnetrons for microwave heating                                                                                               |

| T5   | Cathode-ray tubes Instrument tubes, monitor and display tubes, C.R. tubes for special applications                             |

| Т6   | Geiger-Müller tubes                                                                                                            |

| Т8   | <b>Colour display systems</b> Colour TV picture tubes, colour data graphic display tube assemblies, deflection units           |

| Т9   | Photo and electron multipliers                                                                                                 |

| T 10 | Plumbicon camera tubes and accessories                                                                                         |

| T11  | Microwave semiconductors and components                                                                                        |

| T12  | Vidicon and Newvicon camera tubes                                                                                              |

| T13  | Image intensifiers and infrared detectors                                                                                      |

| T15  | Dry reed switches                                                                                                              |

| T16  | Monochrome tubes and deflection units  Black and white TV picture tubes, monochrome data graphic display tubes, deflection uni |

## SEMICONDUCTORS (RED SERIES)

The red series of data handbooks comprises:

| S1        | Diodes Small-signal silicon diodes, voltage regulator diodes ( $<$ 1,5 W), voltage reference diodes, tuner diodes, rectifier diodes                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S2a       | Power diodes                                                                                                                                                                     |

| S2b       | Thyristors and triacs                                                                                                                                                            |

| <b>S3</b> | Small-signal transistors                                                                                                                                                         |

| S4a       | Low-frequency power transistors and hybrid modules                                                                                                                               |

| S4b       | High-voltage and switching power transistors                                                                                                                                     |

| <b>S5</b> | Field-effect transistors                                                                                                                                                         |

| S6        | R.F. power transistors and modules                                                                                                                                               |

| <b>S7</b> | Surface mounted semiconductors                                                                                                                                                   |

| S8a       | Light-emitting diodes                                                                                                                                                            |

| S8b       | Devices for optoelectronics Optocouplers, photosensitive diodes and transistors, infrared light-emitting diodes and infrared sensitive devices, laser and fibre-optic components |

| <b>S9</b> | Power MOS transistors                                                                                                                                                            |

| S10       | Wideband transistors and wideband hybrid IC modules                                                                                                                              |

| S11       | Microwave transistors                                                                                                                                                            |

| S12       | Surface acoustic wave devices                                                                                                                                                    |

| S13       | Semiconductor sensors                                                                                                                                                            |

| *S14      | Liquid Crystal Displays                                                                                                                                                          |

<sup>\*</sup>To be issued shortly.

## INTEGRATED CIRCUITS (PURPLE SERIES)

The NEW SERIES of handbooks is now completed. With effect from the publication date of this handbook the "N" in the handbook code number will be deleted. Handbooks to be replaced during 1986 are shown below.

The purple series of handbooks comprises:

| • •                 | ·                                                                 |                                 |

|---------------------|-------------------------------------------------------------------|---------------------------------|

| IC01                | Radio, audio and associated systems<br>Bipolar, MOS               | new issue 1986<br>IC01N 1985    |

| IC02a/b             | Video and associated systems<br>Bipolar, MOS                      | new issue 1986<br>IC02Na/b 1985 |

| IC03                | Integrated circuits for telephony Bipolar, MOS                    | new issue 1986<br>IC03N 1985    |

| IC04                | HE4000B logic family CMOS                                         | new issue 1986<br>IC4 1983      |

| IC05N               | HE4000B logic family — uncased ICs CMOS                           | published 1984                  |

| IC06N               | High-speed CMOS; PC74HC/HCT/HCU Logic family                      | published 1986                  |

| IC08                | ECL 10K and 100K logic families                                   | New issue 1986<br>IC08N 1984    |

| IC09N               | TTL logic series                                                  | published 1986                  |

| IC10                | Memories<br>MOS, TTL, ECL                                         | new issue 1986<br>IC7 1982      |

| IC11N               | Linear LSI                                                        | published 1985                  |

| Supplement to IC11N | Linear LSI                                                        | published 1986                  |

| IC12                | I <sup>2</sup> C-bus compatible ICs                               | not yet issued                  |

| IC13                | Semi-custom Programmable Logic Devices (PLD)                      | new issue 1986<br>IC13N 1985    |

| IC14N               | Microprocessors, microcontrollers and peripherals<br>Bipolar, MOS | published 1985                  |

| IC15                | FAST TTL logic series                                             | new issue 1986<br>IC15N 1985    |

| IC16                | CMOS integrated circuits for clocks and watches                   | first issue 1986                |

| IC17                | Integrated Services Digital Networks (ISDN)                       | not yet issued                  |

| IC18                | Microprocessors and peripherals                                   | new issue 1986*                 |

|                     |                                                                   |                                 |

<sup>\*</sup> The Microprocessors were included in handbook IC14N 1985, so IC18 will replace that part of IC14N.

## COMPONENTS AND MATERIALS (GREEN SERIES)

### The green series of data handbooks comprises:

| C2        | relevision tuners, coaxial aerial input assemblies, surface acoustic wave inters |

|-----------|----------------------------------------------------------------------------------|

| C3        | Loudspeakers                                                                     |

| C4        | Ferroxcube potcores, square cores and cross cores                                |

| C5        | Ferroxcube for power, audio/video and accelerators                               |

| <b>C6</b> | Synchronous motors and gearboxes                                                 |

| <b>C7</b> | Variable capacitors                                                              |

| C8        | Variable mains transformers                                                      |

| C9        | Piezoelectric quartz devices                                                     |

| C11       | Varistors, thermistors and sensors                                               |

| C12       | Potentiometers, encoders and switches                                            |

| C13       | Fixed resistors                                                                  |

| C14       | Electrolytic and solid capacitors                                                |

| C15       | Ceramic capacitors                                                               |

| C16       | Permanent magnet materials                                                       |

| C17       | Stepping motors and associated electronics                                       |

| C18       | Direct current motors                                                            |

| C19       | Piezoelectric ceramics                                                           |

| C20       | Wire-wound components for TVs and monitors                                       |

| C22       | Film capacitors                                                                  |

## **SELECTION GUIDE**

| Functional index. |  |  | <br> |  |  | <br> |  |  |  |  |  |  |  |  | <br> |  |  |  | 3 |

|-------------------|--|--|------|--|--|------|--|--|--|--|--|--|--|--|------|--|--|--|---|

| Numerical index . |  |  | <br> |  |  | <br> |  |  |  |  |  |  |  |  | <br> |  |  |  | 5 |

## **FUNCTIONAL INDEX**

| type number             | description                                                | page |

|-------------------------|------------------------------------------------------------|------|

| CMOS RAM                |                                                            | -    |

| PCD5101                 | 256 x 4-bit static RAM                                     | 19   |

| PCD5114                 | 1024 x 4-bit static RAM                                    | 27   |

| PCF8570                 | 256 x 8-bit static RAM with I <sup>2</sup> C bus interface | 35   |

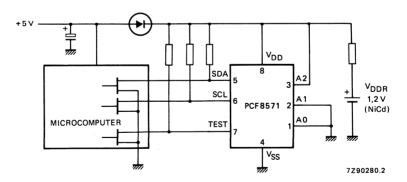

| PCF8571                 | 128 x 8-bit static RAM                                     | 47   |

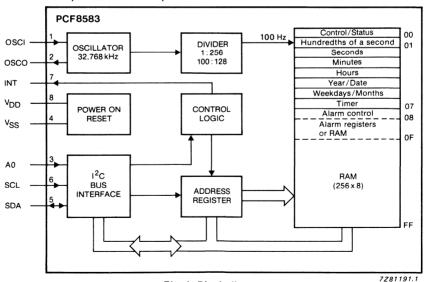

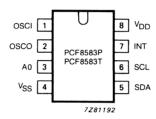

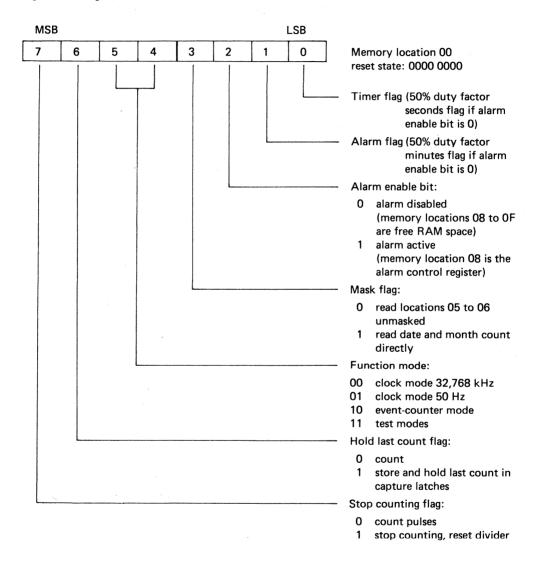

| PCF8583                 | 256 x 8-bit static RAM                                     | 59   |

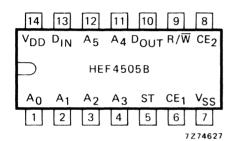

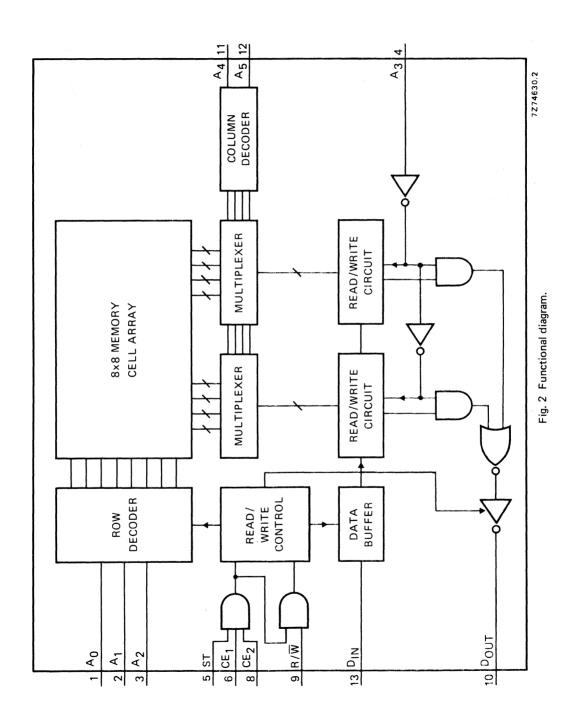

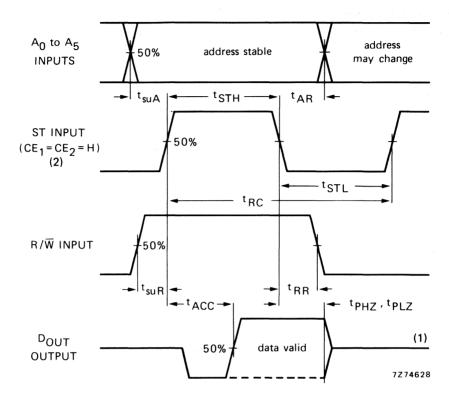

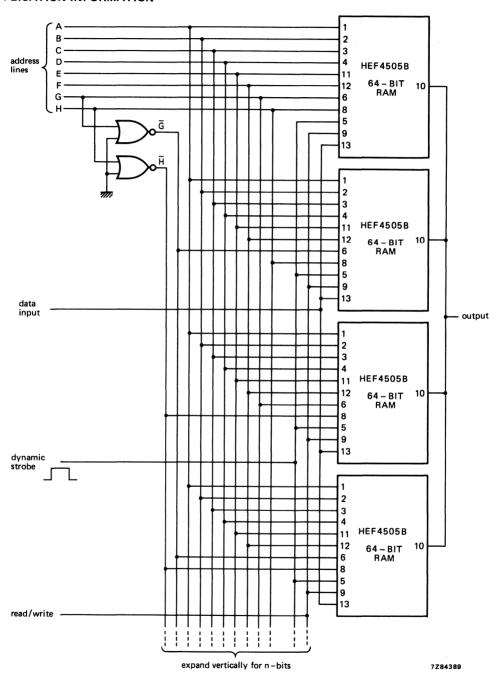

| HEF4505B                | 64-bit, 1-bit per word R/W RAM                             | 77   |

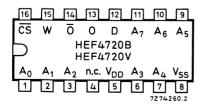

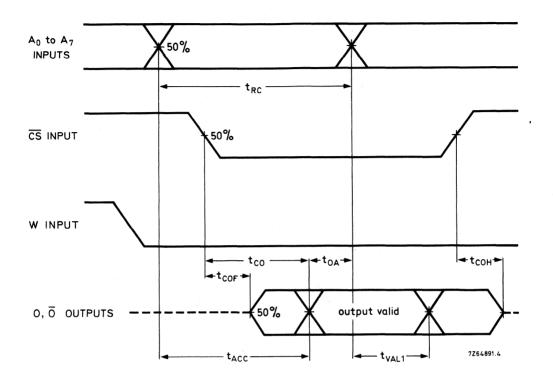

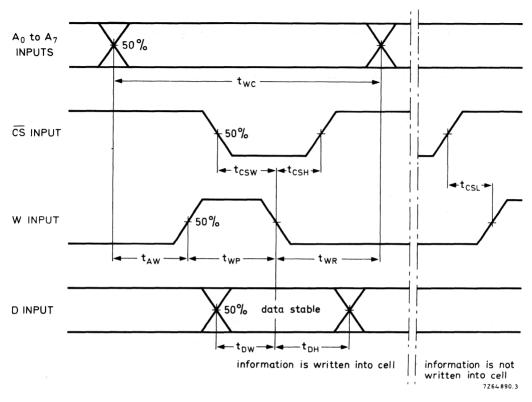

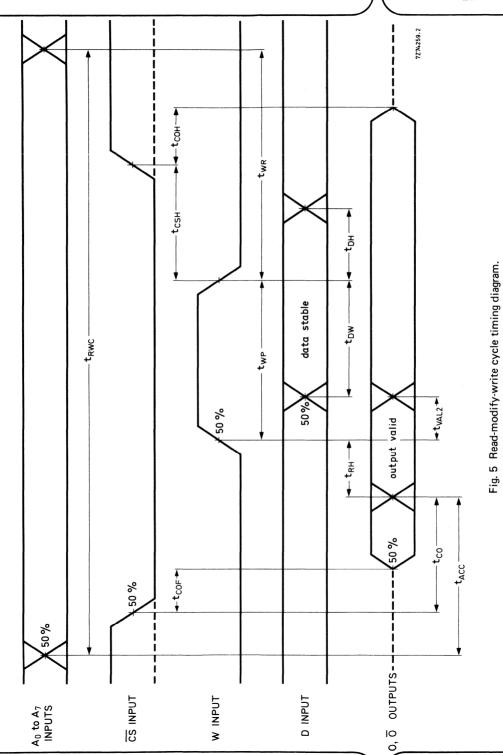

| HEF4720B; V             | 256-bit, 1-bit per word RAM                                | 85   |

| SBB6116L-10             | 2048 x 8-bit static RAM; max. access time 100 ns           | 101  |

| SBB6116L-12             | 2048 x 8-bit static RAM; max. access time 120 ns           | 101  |

| CMOS EEPROM             |                                                            |      |

| PCB8582                 | Static CMOS EEPROM (256 x 8)                               | 113  |

| Charge-Coupled Memory   |                                                            |      |

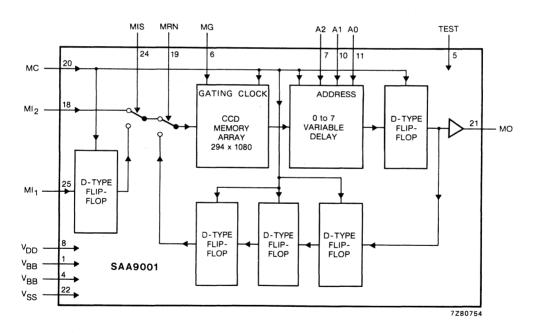

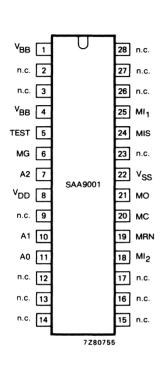

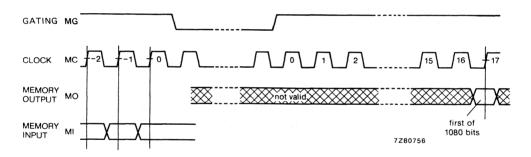

| SAA9001                 | 317K-bit CCD memory                                        | 123  |

| 64-bit TTL Bipolar RAM  |                                                            |      |

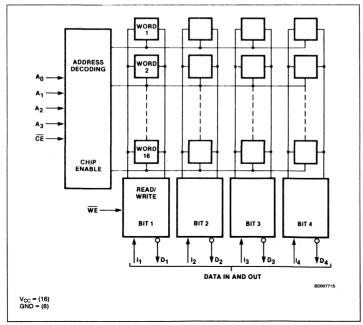

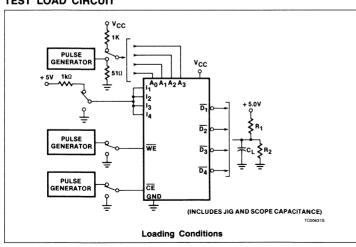

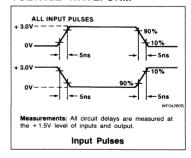

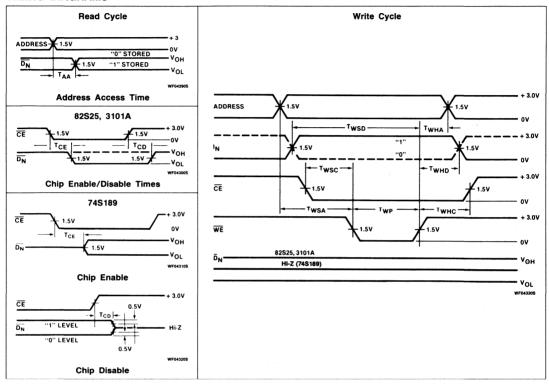

| 82S25                   | 64-bit Bipolar RAM (16 x 4)                                | 149  |

| 3101A                   | 64-bit Bipolar RAM (16 x 4)                                | 149  |

| 74F189                  | 64-bit Bipolar RAM (16 x 4)                                | 153  |

| 74S189                  | 64-bit Bipolar RAM (16 x 4)                                | 149  |

| 256-bit TTL Bipolar RAM |                                                            |      |

| 82\$16                  | 256-bit Bipolar RAM (256 x 1)                              | 159  |

| 82LS16                  | 256-bit Bipolar RAM (256 x 1)                              | 163  |

| 74S301                  | 256-bit Bipolar RAM (256 x 1)                              | 167  |

| 74LS301                 | 256-bit Bipolar RAM (256 x 1)                              | 171  |

| Byte-Organized RAM      |                                                            |      |

| 82S09/82S09A            | 576-bit Bipolar RAM (64 x 9)                               | 177  |

| 82\$19                  | 576-bit Bipolar RAM (64 x 9)                               | 181  |

| 82S212/82 <b>S212A</b>  | 2304-bit Bipolar RAM (256 x 9)                             | 185  |

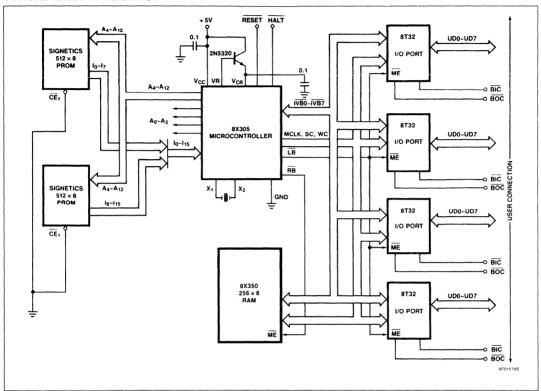

| 8X350                   | 2048-bit Bipolar RAM (256 x 8)                             | 189  |

# FUNCTIONAL INDEX

| type number                                                        | description                                                                                                                                                                      | page                            |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Low Complexity PROM                                                |                                                                                                                                                                                  |                                 |

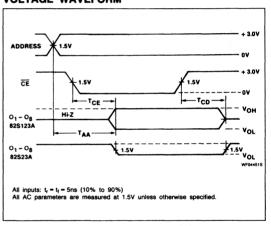

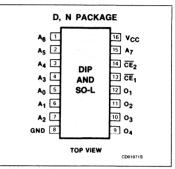

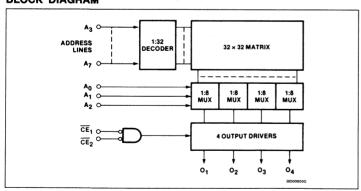

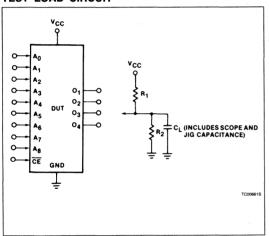

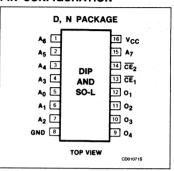

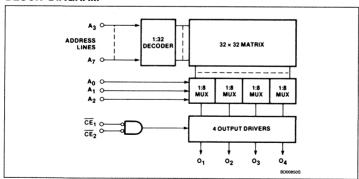

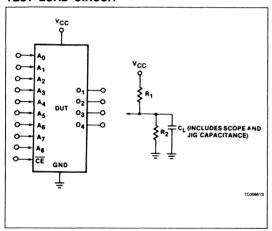

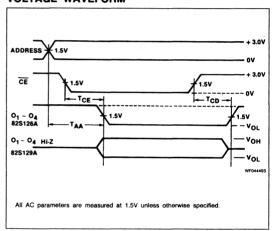

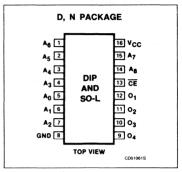

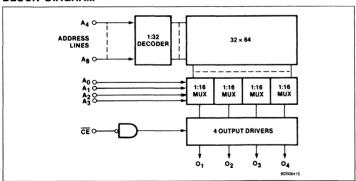

| 82S23/82S123<br>82S23A/82S123A<br>82S126/82S129<br>82S126A/82S129A | 256-bit Bipolar PROM (32 x 8)<br>256-bit Bipolar PROM (32 x 8)<br>1024-bit Bipolar PROM (256 x 4)<br>1024-bit Bipolar PROM (256 x 4)                                             | 201<br>204<br>207<br>210        |

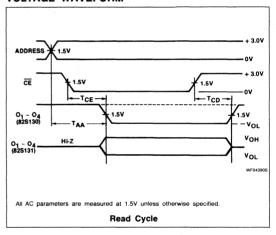

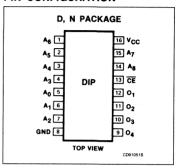

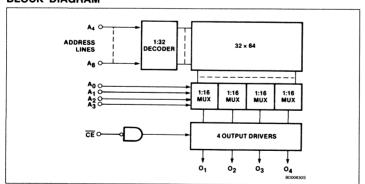

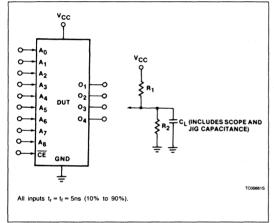

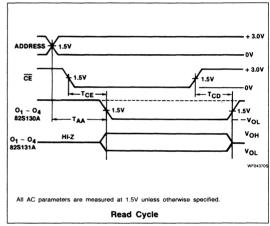

| 82S130/82S131<br>82S130A/82S131A<br>82S135<br>82LS135              | 2048-bit Bipolar PROM (512 x 4) 2048-bit Bipolar PROM (512 x 4) 2048-bit Bipolar PROM (256 x 8) 2048-bit Bipolar PROM (256 x 8)                                                  | 213<br>216<br>219<br>222        |

| 4K-bit TTL Bipolar PROM                                            |                                                                                                                                                                                  |                                 |

| 82S115<br>82S137<br>82S137A/82S137B<br>82S147/82S147A              | 4096-bit Bipolar PROM (512 x 8)<br>4096-bit Bipolar PROM (1024 x 4)<br>4096-bit Bipolar PROM (1024 x 4)<br>4096-bit Bipolar PROM (512 x 8)                                       | 227<br>231<br>234<br>237        |

| 8K-bit TTL Bipolar PROM                                            |                                                                                                                                                                                  |                                 |

| 82S181<br>82S181C<br>82LS181<br>82S183<br>82S185                   | 8192-bit Bipolar PROM (1024 x 8)<br>8192-bit Bipolar PROM (2048 x 4) | 243<br>246<br>249<br>252<br>256 |

| 82S185A/82S185B<br>82HS187/82HS187A<br>82HS189/82HS189A            | 8192-bit Bipolar PROM (2048 x 4)<br>8192-bit Bipolar PROM (1024 x 8)<br>8192-bit Bipolar PROM (1024 x 8)                                                                         | 259<br>262<br>266               |

| 16K-bit TTL Bipolar PROM                                           |                                                                                                                                                                                  |                                 |

| 82S191/82S191A<br>82S191C<br>82HS195/82HS195A/82HS195B             | 16,384-bit Bipolar PROM (2048 x 8)<br>16,384-bit Bipolar PROM (2048 x 8)<br>16,384-bit Bipolar PROM (4096 x 4)                                                                   | 273<br>276<br>279               |

| 32K-bit TTL Bipolar PROM                                           |                                                                                                                                                                                  |                                 |

| 82S321<br>82HS321/82HS321A/82HS321B                                | 32,768-bit Bipolar PROM (4096 x 8)<br>32,768-bit Bipolar PROM (4096 x 8)                                                                                                         | 285<br>288                      |

| <b>64K-bit TTL Bipolar PROM</b><br>82HS641/82HS641A/82HS641B       | 65,536-bit Bipolar PROM (8192 x 8)                                                                                                                                               | 293                             |

| Bipolar ECL RAM                                                    |                                                                                                                                                                                  |                                 |

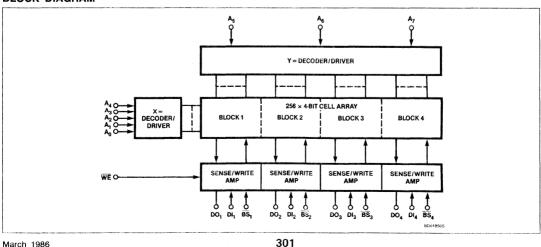

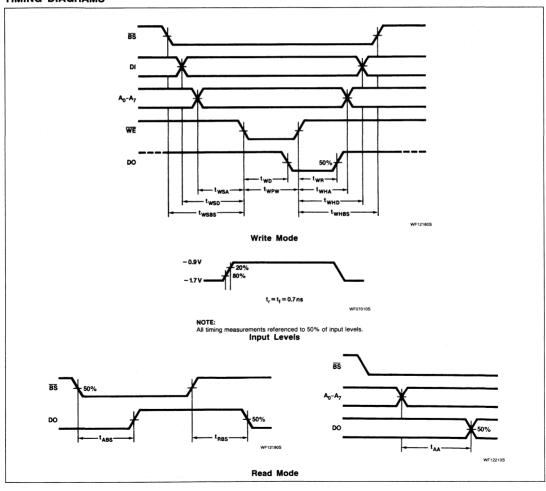

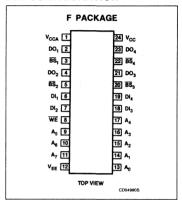

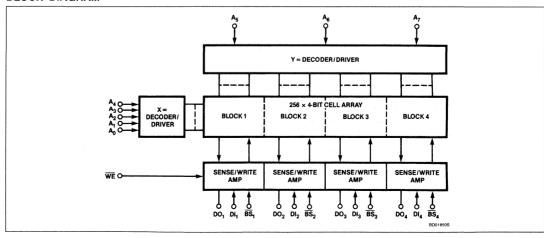

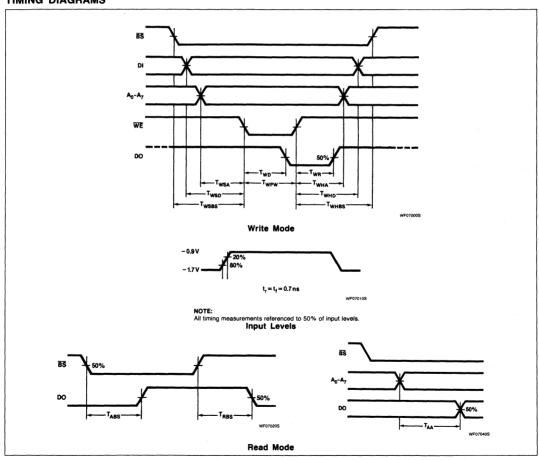

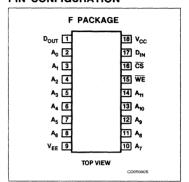

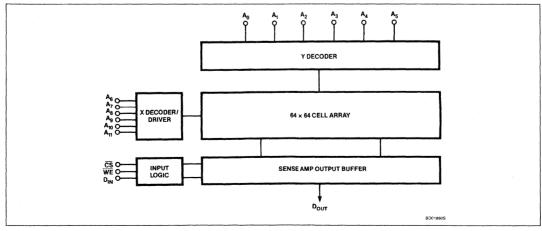

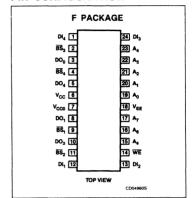

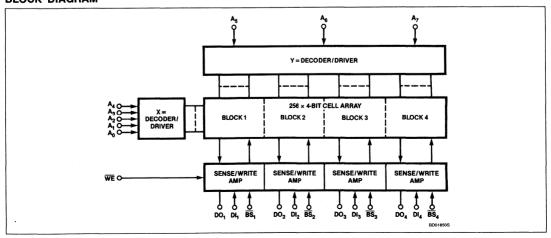

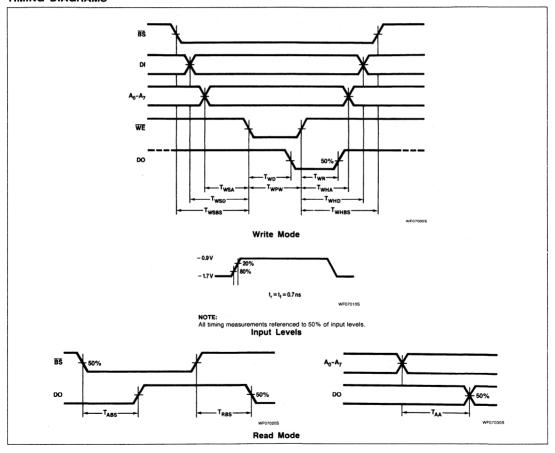

| 10422B<br>10422C<br>10470A<br>100422B<br>100422C                   | 256 x 4-bit RAM<br>256 x 4-bit RAM<br>4096 x 1-bit RAM<br>256 x 4-bit RAM<br>256 x 4-bit RAM                                                                                     | 301<br>304<br>307<br>310<br>313 |

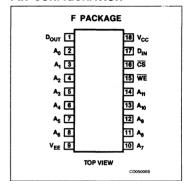

| 100470A<br>100474A                                                 | 4096 x 1-bit RAM<br>1024 x 4-bit RAM                                                                                                                                             | 316<br>319                      |

## NUMERICAL INDEX

| type number               | description                                                | page |

|---------------------------|------------------------------------------------------------|------|

| HEF4505B                  | 64-bit, 1-bit per word R/W RAM                             | 77   |

| HEF4720B; V               | 256-bit, 1-bit per word RAM                                | 85   |

| PCB8582                   | Static CMOS EEPROM (256 x 8)                               | 113  |

| PCD5101                   | 256 x 4-bit static RAM                                     | 19   |

| PCD5114                   | 1024 x 4-bit static RAM                                    | 27   |

| PCF8570                   | 256 x 8-bit static RAM with I <sup>2</sup> C bus interface | 35   |

| PCF8571                   | 128 x 8-bit static RAM                                     | 47   |

| PCF8583                   | 256 x 8-bit static RAM                                     | 59   |

| SAA9001                   | 317K-bit CCD memory                                        | 123  |

| SBB6116L-10               | 2048 x 8-bit static RAM; max. access time 100 ns           | 101  |

| SBB6116L-12               | 2048 x 8-bit static RAM; max. access time 120 ns           | 101  |

| 8X350                     | 2048-bit Bipolar RAM (256 x 8)                             | 189  |

| 74F189                    | 64-bit Bipolar RAM (16 x 4)                                | 153  |

| 74LS301                   | 256-bit Bipolar RAM (256 x 1)                              | 171  |

| 74S189                    | 64-bit Bipolar RAM (16 x 4)                                | 149  |

| 74S301                    | 256-bit Bipolar RAM (256 x 1)                              | 167  |

| 82HS187/82HS187A          | 8192-bit Bipolar PROM (1024 x 8)                           | 262  |

| 82HS189/82HS189A          | 8192-bit Bipolar PROM(1024 x 8)                            | 266  |

| 82HS195/82HS195A/82HS195B | 16,384-bit Bipolar PROM (4096 x 4)                         | 279  |

| 82HS321/82HS321A/82HS321B | 32,768-bit Bipolar PROM (4096 x 8)                         | 288  |

| 82HS641/82HS641A/82HS641B | 65,536-bit Bipolar PROM (8192 x 8)                         | 293  |

| 82LS16                    | 256-bit Bipolar RAM (256 x 1)                              | 163  |

| 82LS135                   | 2048-bit Bipolar PROM (256 x 8)                            | 222  |

| 82LS181                   | 8192-bit Bipolar PROM (1024 x 8)                           | 249  |

| 82S09/82S09A              | 576-bit Bipolar RAM (64 x 9)                               | 177  |

| 82S16                     | 256-bit Bipolar RAM (256 x 1)                              | 159  |

| 82S19                     | 576-bit Bipolar RAM (64 x 9)                               | 181  |

| 82S23/82S123              | 256-bit Bipolar PROM (32 x 8)                              | 201  |

| 82S23A/82S123A            | 256-bit Bipolar PROM (32 x 8)                              | 204  |

| 82S25                     | 64-bit Bipolar RAM (16 x 4)                                | 149  |

| 82S115                    | 4096-bit Bipolar PROM (512 x 8)                            | 227  |

| 82S126/82S129             | 1024-bit Bipolar PROM (256 x 4)                            | 207  |

| 82S126A/82S129A           | 1024-bit Bipolar PROM (256 x 4)                            | 210  |

| 82S130/82S131             | 2048-bit Bipolar PROM (512 x 4)                            | 213  |

| 82S130A/82S131A           | 2048-bit Bipolar PROM (512 x 4)                            | 216  |

| 82S135                    | 2048-bit Bipolar PROM (256 x 8)                            | 219  |

| 82S137                    | 4096-bit Bipolar PROM (1024 x 4)                           | 231  |

| 82S137A/82S137B           | 4096-bit Bipolar PROM (1024 x 4)                           | 234  |

| 82S147/82S147A            | 4096-bit Bipolar PROM (512 $\times$ 8)                     | 237  |

| 82S181                    | 8192-bit Bipolar PROM (1024 x 8)                           | 243  |

# NUMERICAL INDEX

| type number     | description                        | page |

|-----------------|------------------------------------|------|

| 82S181C         | 8192-bit Bipolar PROM (1024 x 8)   | 246  |

| 82S183          | 8192-bit Bipolar PROM (1024 x 8)   | 252  |

| 82S185          | 8192-bit Bipolar PROM (2048 x 4)   | 256  |

| 82S185A/82S185B | 8192-bit Bipolar PROM (2048 x 4)   | 259  |

| 82S191/82S191A  | 16,384-bit Bipolar PROM (2048 x 8) | 273  |

| 82S191C         | 16,384-bit Bipolar PROM (2048 x 8) | 276  |

| 82S212/82S212A  | 2304-bit Bipolar RAM (256 x 9)     | 185  |

| 82S321          | 32,768-bit Bipolar PROM (4096 x 8) | 285  |

| 3101A           | 64-bit Bipolar RAM (16 x 4)        | 149  |

| 10422B          | 256 x 4-bit RAM                    | 301  |

| 10422C          | 256 x 4-bit RAM                    | 304  |

| 10470A          | 4096 x 1-bit RAM                   | 307  |

| 100422B         | 256 x 4-bit RAM                    | 310  |

| 100422C         | 256 x 4-bit RAM                    | 313  |

| 100470; A       | 4096 x 1-bit RAM                   | 316  |

| 100474A         | 1024 x 4-bit RAM                   | 319  |

## MOS MEMORIES

| ntroduction          | 1  |

|----------------------|----|

| MOS RAM              |    |

| MOS EEPROM           | 11 |

| harge-Coupled Memory | 12 |

## Introduction

| Type designation     | 13 |

|----------------------|----|

| Rating systems       | 15 |

| Handling MOS devices | 16 |

## PRO ELECTRON TYPE DESIGNATION CODE FOR INTEGRATED CIRCUITS

This type nomenclature applies to semiconductor monolithic, semiconductor multi-chip, thin-film, thick-film and hybrid integrated circuits.

A basic type number consists of:

THREE LETTERS FOLLOWED BY A SERIAL NUMBER

### FIRST AND SECOND LETTER

1. DIGITAL FAMILY CIRCUITS

The FIRST TWO LETTERS identify the FAMILY (see note 1).

2. SOLITARY CIRCUITS

The FIRST LETTER divides the solitary circuits into:

S: Solitary digital circuits

T: Analogue circuits

U: Mixed analogue/digital circuits

The SECOND LETTER is a serial letter without any further significance except 'H' which stands for hybrid circuits (see note 3).

3. MICROPROCESSORS

The FIRST TWO LETTERS identify microprocessors and correlated circuits as follows:

Microcomputer

Central processing unit

MB : Slice processor (see note 2)

MD: Correlated memoriesME: Other correlated circuits (interface, clock, peripheral controller, etc.)

4. CHARGE-TRANSFER DEVICES AND SWITCHED CAPACITORS

The FIRST TWO LETTERS identify the following:

NH: Hybrid circuits

NL: Logic circuits

NM: Memories

NS: Analogue signal processing, using switched capacitors

NT: Analogue signal processing, using CTDs

NX: Imaging devices

NY: Other correlated circuits

### Notes

- A logic family is an assembly of digital circuits designed to be interconnected and defined by its basic electrical characteristics (such as: supply voltage, power consumption, propagation delay, noise immunity).

- 2. By 'slice processor' is meant: a functional slice of microprocessor.

- 3. The first letter 'S' should be used for all solitary memories, to which, in the event of hybrids, the second letter 'H' should be added (e.g. SH for Bubble-memories).

## TYPE DESIGNATION

### THIRD LETTER

It indicates the operating ambient temperature range.

The letters A to G give information about the temperature:

A: temperature range not specified

$\begin{array}{lll} B : & 0 \text{ to} + 70 \text{ }^{\circ}\text{C} \\ \text{C} : & -55 \text{ to} + 125 \text{ }^{\circ}\text{C} \\ \text{D} : & -25 \text{ to} + 70 \text{ }^{\circ}\text{C} \\ \text{E} : & -25 \text{ to} + 85 \text{ }^{\circ}\text{C} \\ \text{F} : & -40 \text{ to} + 85 \text{ }^{\circ}\text{C} \\ \text{G} : & -55 \text{ to} + 85 \text{ }^{\circ}\text{C} \end{array}$

If a circuit is published for another temperature range, the letter indicating a narrower temperature range may be used or the letter 'A'.

Example: the range 0 to + 75 °C can be indicated by 'B' or 'A'.

### SERIAL NUMBER

This may be either a 4-digit number assigned by Pro Electron, or the serial number (which may be a combination of figures and letters) of an existing company type designation of the manufacturer.

To the basic type number may be added:

### A VERSION LETTER

Indicates a minor variant of the basic type or the package. Except for 'Z', which means customized wiring, the letter has no fixed meaning. The following letters are recommended for package variants:

C: for cylindrical

D: for ceramic DIL

F: for flat pack

L: for chip on tape

P: for plastic DIL

Q: for QIL

T: for miniature plastic (mini-pack)

U: for uncased chip

Alternatively a TWO LETTER SUFFIX may be used instead of a single package version letter, if the manufacturer (sponsor) wishes to give more information.

FIRST LETTER: General shape

SECOND LETTER: Material

C : Cylindrical C : Metal-ceramic

D: Dual-in-line (DIL)

G: Glass-ceramic (cerdip)

E: Power DIL (with external heatsink)

M: Metal

F: Flat (leads on 2 sides)

F: Flat (leads on 4 sides)

P: Plastic

K: Diamond (TO-3 family)

M: Multiple-in-line (except Dual-, Triple-, Quadruple-in-line)

Q: Quadruple-in-line (QIL)

R: Power QIL (with external heatsink)

S : Single-in-line T : Triple-in-line

W: Lead chip-carrier (LCC)

X: Leadless chip-carrier (LLCC)

X: Leadless chip-carrier (LLCC)

Y: Pin grid array (PGA)

A hyphen precedes the suffix to avoid confusion with a version letter.

#### **RATING SYSTEMS**

The rating systems described are those recommended by the International Electrotechnical Commission (IEC) in its Publication 134.

## **DEFINITIONS OF TERMS USED Electronic device.**

An electronic tube or valve, transistor or other semiconductor device.

Note: This definition excludes inductors, capacitors, resistors and similar components.

#### Characteristic

A characteristic is an inherent and measurable property of a device. Such a property may be electrical, mechanical, thermal, hydraulic, electro-magnetic, or nuclear, and can be expressed as a value for stated or recognized conditions. A characteristic may also be a set of related values, usually shown in graphical form.

### **Bogev electronic device**

An electronic device whose characteristics have the published nominal values for the type. A bogey electronic device for any particular application can be obtained by considering only those charactersistics which are directly related to the application.

### Rating

A value which establishes either a limiting capability or a limiting condition for an electronic device. It is determined for specified values of environment and operation, and may be stated in any suitable terms.

Note: Limiting conditions may be either maxima or minima.

### **Rating system**

The set of principles upon which ratings are established and which determine their interpretation.

Note: The rating system indicates the division of responsibility between the device manufacturer and the circuit designer, with the object of ensuring that the working conditions do not exceed the ratings.

### **ABSOLUTE MAXIMUM RATING SYSTEM**

Absolute maximum ratings are limiting values of operating and environmental conditions applicable to any electronic device of a specified type as defined by its published data, which should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in the characteristics of the device under consideration and of all other electronic devices in the equipment.

The equipment manufacturer should design so that, initially and throughout life, no absolute maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variations, signal variation, environmental conditions, and variations in characteristics of the device under consideration and of all other electronic devices in the equipment.

### **DESIGN MAXIMUM RATING SYSTEM**

Design maximum ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking responsibility for the effects of changes in operating conditions due to variations in the characteristics of the electronic device under consideration.

The equipment manufacturer should design so that, initially and throughout life, no design maximum value for the intended service is exceeded with a bogey device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, variation in characteristics of all other devices in the equipment, equipment control adjustment, load variation, signal variation and environmental conditions

### **DESIGN CENTRE RATING SYSTEM**

Design centre ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under normal conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device in average applications, taking responsibility for normal changes in operating conditions due to rated supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in characteristics of all electronic devices.

The equipment manufacturer should design so that, initially, no design centre value for the intended service is exceeded with a bogey electronic device in equipment operating at the stated normal supply voltage.

## HANDLING MOS DEVICES

#### HANDLING MOS DEVICES

Though all our MOS integrated circuits incorporate protection against electrostatic discharges, they can nevertheless be damaged by accidental over-voltages. In storing and handling them, the following precautions are recommended.

### Caution

Testing or handling and mounting call for special attention to personal safety. Personnel handling MOS devices should normally be connected to ground via a resistor.

### Storage and transport

Store and transport the circuits in their original packing. Alternatively, use may be made of a conductive material or special IC carrier that either short-circuits all leads or insulates them from external contact.

### Testing or handling

Work on a conductive surface (e.g. metal table top) when testing the circuits or transferring them from one carrier to another. Electrically connect the person doing the testing or handling to the conductive surface, for example by a metal bracelet and a conductive cord or chain. Connect all testing and handling equipment to the same surface.

Signals should not be applied to the inputs while the device power supply is off. All unused input leads should be connected to either the supply voltage or ground.

### Mounting

Mount MOS integrated circuits on printed circuit boards *after* all other components have been mounted. Take care that the circuits themselves, metal parts of the board, mounting tools, and the person doing the mounting are kept at the same electric (ground) potential. If it is impossible to ground the printed-circuit board the person mounting the circuits should touch the board before bringing MOS circuits into contact with it.

### Soldering

Soldering iron tips, including those of low-voltage irons, or soldering baths should also be kept at the same potential as the MOS circuits and the board.

### Static charges

Dress personnel in clothing of non-electrostatic material (no wool, silk or synthetic fibres). After the MOS circuits have been mounted on the board proper handling precautions should still be observed. Until the sub-assemblies are inserted into a complete system in which the proper voltages are supplied, the board is no more than an extension of the leads of the devices mounted on the board. To prevent static charges from being transmitted through the board wiring to the device it is recommended that conductive clips or conductive tape be put on the circuit board terminals.

### Transient voltages

To prevent permanent damage due to transient voltages, do not insert or remove MOS devices, or printed-circuit boards with MOS devices, from test sockets or systems with power on.

### Voltage surges

Beware of voltage surges due to switching electrical equipment on or off, relays and d.c. lines.

## **CMOS RAM**

| PCD5101         | 256 x 4-bit static RAM         | 19  |

|-----------------|--------------------------------|-----|

| PCD5114         | 1024 x 4-bit static RAM        | 27  |

| PCF8570         | 256 x 8-bit static RAM         | 35  |

| PCF8571         | 128 x 8-bit static RAM         | 47  |

| PCF8583         | 256 x 8-bit static RAM         | 59  |

| HEF4505B        | 64-bit, 1-bit per word R/W RAM | 77  |

| HEF4720B; V     | 256-bit, 1-bit per word RAM    | 85  |

| SBB6116L-10; 12 | 2048 x 8-bit static RAM        | 101 |

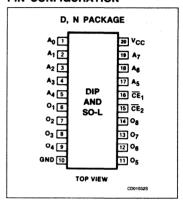

### 256 × 4-BIT STATIC RAM

### **GENERAL DESCRIPTION**

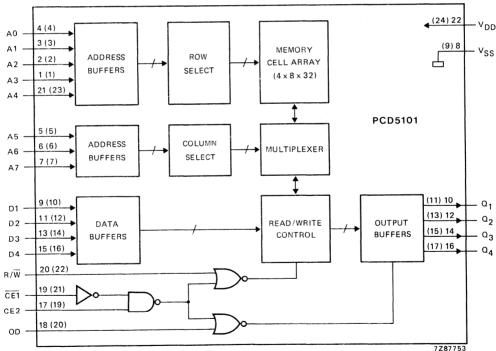

The PCD5101 is a very low-power 1024-bit static CMOS random access memory, organized as 256 words by 4 bits. It is suitable for low power and high speed applications where battery standby power is required to ensure non-volatility of data. All inputs and outputs are fully TTL compatible and pinning is compatible with 2101-type NMOS static RAMs and 5101-type CMOS static RAMs.

There are two chip enable inputs,  $\overline{CE1}$  and  $\overline{CE2}$ , selection being made when  $\overline{CE1}$  is LOW and  $\overline{CE2}$  is HIGH. The memory has an output disable function, OD, which allows the inputs/outputs to be used separately, or to be tied together for use in common data I/O systems.

### **Features**

Operating supply voltage range

2,5 to 5,5 V

- Low data retention voltage

- Low power consumption in both operating and standby modes

- Access time 150 ns at V<sub>DD</sub> = 5 V; 400 ns at V<sub>DD</sub> = 3 V

- Three-state outputs

- All inputs and outputs directly TTL compatible

- Choice of two package types

Fig. 1 Block diagram: pin numbers in parentheses are for PCD5101T; other pin numbers are applicable to PCD5101P.

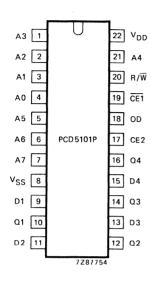

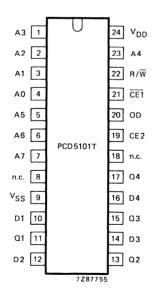

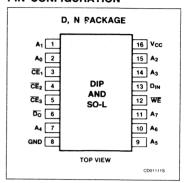

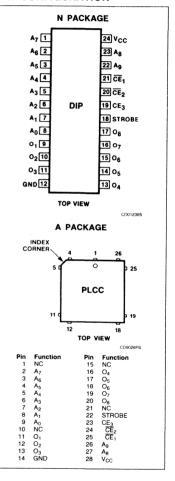

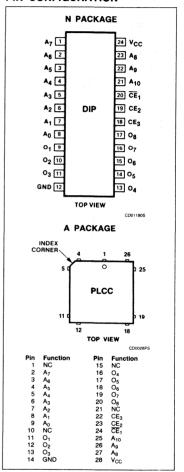

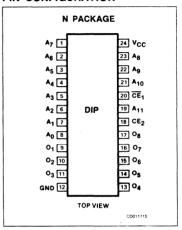

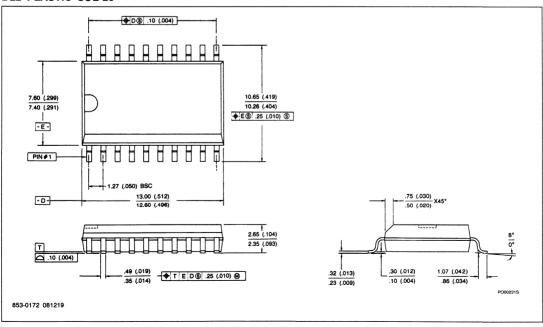

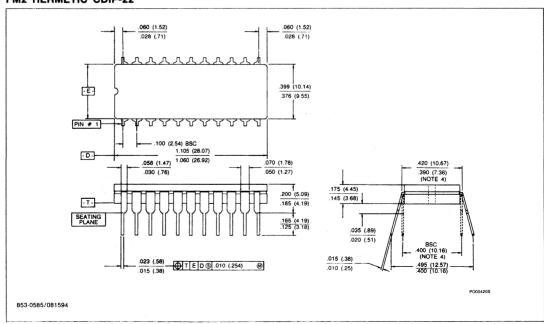

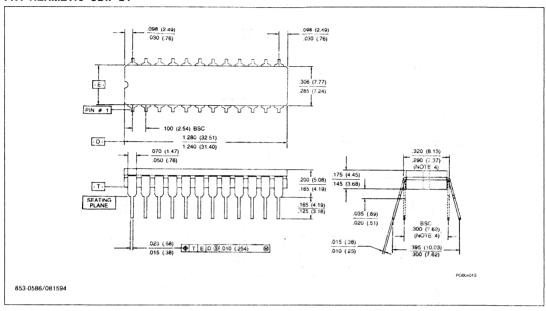

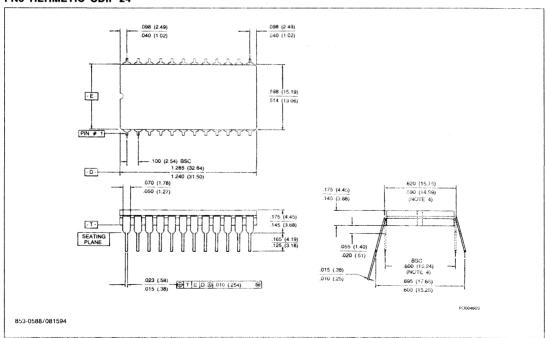

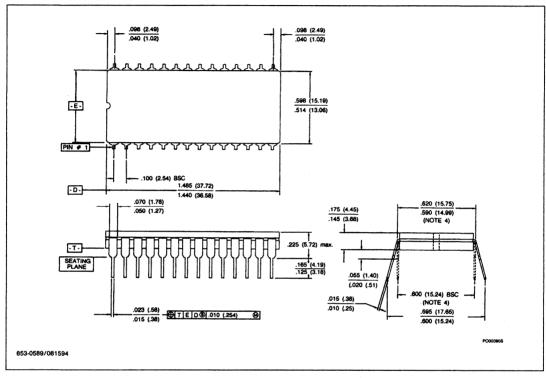

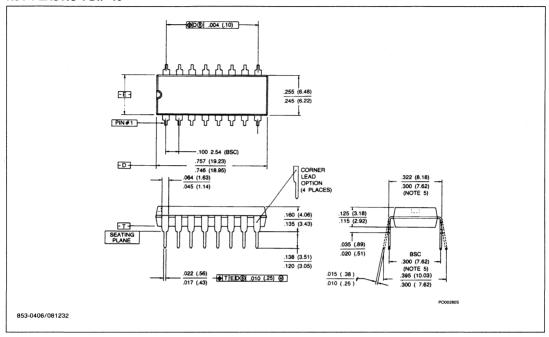

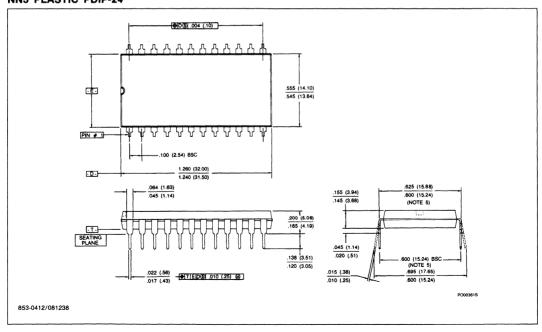

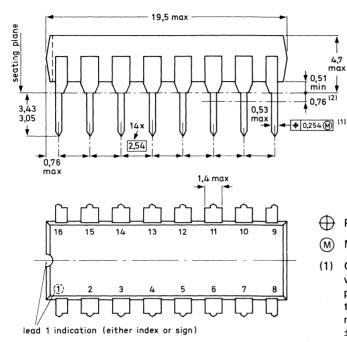

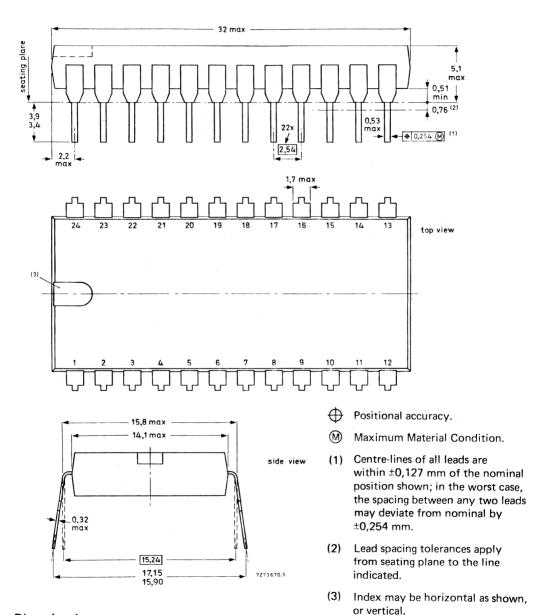

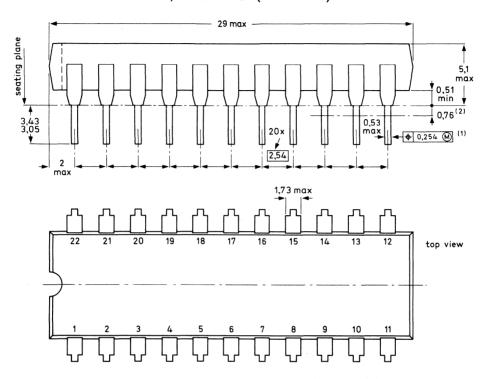

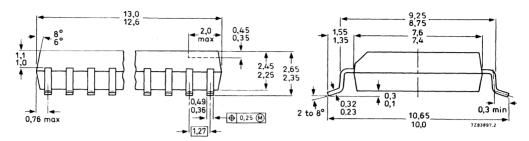

### PACKAGE OUTLINES

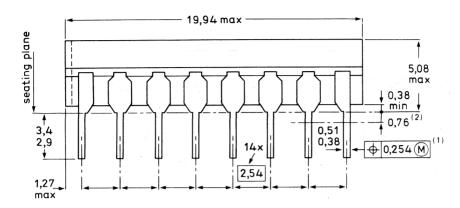

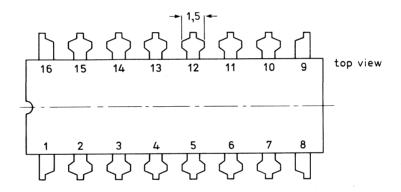

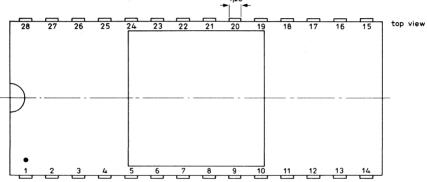

PCD5101P: 22-lead DIL; plastic (SOT-116).

PCD5101T: 24-lead mini-pack, plastic (SO-24; SOT-137A).

Fig. 2 Pinning diagram for PCD5101P.

Fig. 3 Pinning diagram for PCD5101T.

### **OPERATING MODES**

Table 1 Mode selection

| CE1 | CE2 | R/W | OD | mode of operation | output state        |

|-----|-----|-----|----|-------------------|---------------------|

| Н   | Х   | Х   | Х  | standby           | high impedance      |

| X   | L   | X   | X  | standby           | high impedance      |

| L   | Н   | L   | Н  | write             | high impedance      |

| L   | Н   | L   | L  | write             | equal to input data |

| L   | Н   | Н   | L  | read              | data valid          |

| L   | Н   | Н   | Н  | read              | high impedance      |

Separate input/output: write cycle OD = X; read cycle OD = L. Common input/output: write cycle OD = H; read cycle OD = L.

H = HIGH voltage level L = LOW voltage level

X = don't care

### **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage range          | $v_{DD}$  | −0,3 to 8,0 V                          |

|-------------------------------|-----------|----------------------------------------|

| Input voltage range (any pin) | VI        | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ V     |

| Operating temperature range   | $T_{amb}$ | $-25 \text{ to } +70 ^{\circ}\text{C}$ |

| Storage temperature range     | $T_{stg}$ | −55 to +125 °C                         |

### D.C. CHARACTERISTICS (V<sub>DD</sub> = 5 V)

$V_{DD}$  = 5 ± 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to +70 °C

| parameter                                                                                                 | symbol               | min. | typ. | max.                 | unit |

|-----------------------------------------------------------------------------------------------------------|----------------------|------|------|----------------------|------|

| Operating supply voltage                                                                                  | V <sub>DD</sub>      | 4,5  | 5,0  | 5,5                  | ٧    |

| Operating supply current at V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub> ; f = 1 MHz; outputs open | I <sub>DD</sub>      | _    | 10   | 17                   | mA   |

| at V <sub>I</sub> = 0,8 or 2,0 V; f = 1 MHz;<br>outputs open                                              | IDD                  | _    | 10   | 17                   | mA   |

| at V <sub>I</sub> = 0,8 or 2,0 V; f = 5 MHz;<br>outputs open                                              | I <sub>DD</sub>      |      | 12   | 20                   | mA   |

| Standby supply current at CE2 = V <sub>SS</sub>                                                           | ISB                  | _    | 0,02 | 5,0                  | μΑ   |

| Input leakage current<br>at V <sub>I</sub> = V <sub>SS</sub> to V <sub>DD</sub>                           | <br>    <sub> </sub> |      | _    | 0,1                  | μΑ   |

| Input voltage LOW                                                                                         | VIL                  | -0,3 | _    | + 0,8                | V    |

| Input voltage HIGH                                                                                        | VIH                  | 2,0  | _    | V <sub>DD</sub> +0,3 | ٧    |

| Output leakage current<br>at V <sub>O</sub> = V <sub>SS</sub> to V <sub>DD</sub> ;                        |                      |      |      |                      |      |

| OD = HIGH or chip disabled                                                                                | lor                  | _    |      | 0,2                  | μΑ   |

| Output voltage LOW at $I_{OL} = 4.0 \text{ mA}$                                                           | VOL                  | _    | _    | 0,4                  | ٧    |

| Output voltage HIGH at $-I_{OH} = 2,0 \text{ mA}$                                                         | Vон                  | 2,4  | _    | _                    | V    |

### D.C. CHARACTERISTICS (V<sub>DD</sub> = 3 V)

$V_{DD}$  = 3 ± 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to +70 °C

| parameter                                                                                                                                                    | symbol          | min.   | typ. | max.                 | unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|------|----------------------|----------|

| Operating supply voltage                                                                                                                                     | V <sub>DD</sub> | 2,5    | 3,0  | 3,5                  | ٧        |

| Operating supply current at V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub> ; f = 1 MHz; outputs open                                                    | I <sub>DD</sub> | _      | 5    | 8                    | mA       |

| at V <sub>I</sub> = 0,4 or 1,6 V; f = 1 MHz;<br>outputs open                                                                                                 | l <sub>DD</sub> | _      | 5    | 8                    | mA       |

| Standby supply current at CE2 = V <sub>SS</sub>                                                                                                              | ISB             | _      | 0,02 | 5,0                  | μΑ       |

| Input leakage current at V <sub>I</sub> = V <sub>SS</sub> to V <sub>DD</sub>                                                                                 | HILL            | _      | _    | 0,1                  | μΑ       |

| Input voltage LOW                                                                                                                                            | VIL             | -0,3   | _    | +0,4                 | V        |

| Input voltage HIGH                                                                                                                                           | VIН             | 1,6    |      | V <sub>DD</sub> +0,3 | V        |

| Output leakage current  at V <sub>O</sub> = V <sub>SS</sub> to V <sub>DD</sub> ;  OD = HIGH or chip disabled  Output voltage LOW at I <sub>OL</sub> = 1,0 mA | llor!           | -<br>- | _    | 0,2<br>0,3           | μA<br>V  |

| Output voltage LOW at $IOL = 1,0 \text{ mA}$                                                                                                                 | V <sub>OL</sub> | 1,7    |      | -                    | <b>V</b> |

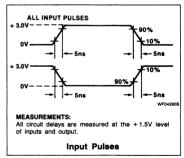

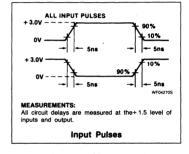

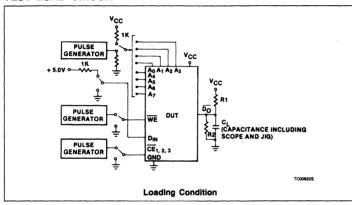

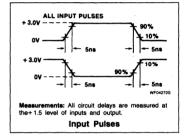

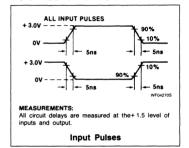

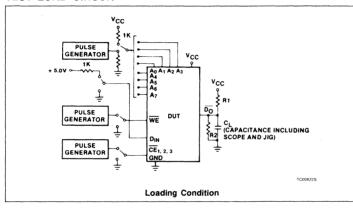

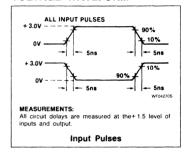

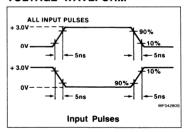

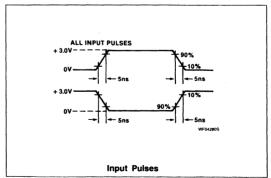

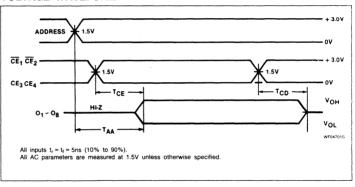

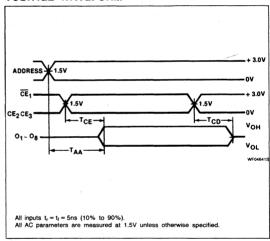

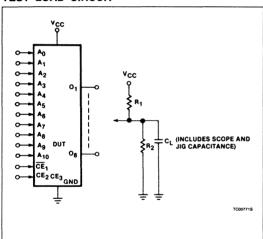

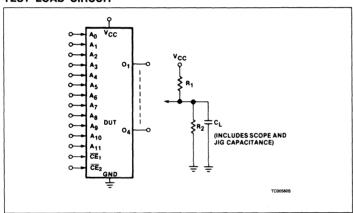

### A.C. TEST CONDITIONS (V<sub>DD</sub> = 5 V)

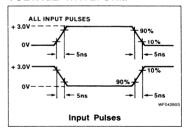

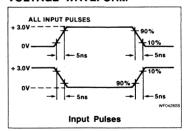

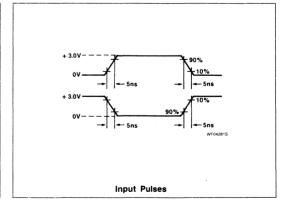

0,8 V to 2,0 V Input pulse levels

Input rise and fall times 5 ns

Input timing reference levels 1,5 V Output timing levels 1,5 V

Output timing levels for high/low

impedance

1,2 V and 2,8 V

Output load (2 TTL inputs and

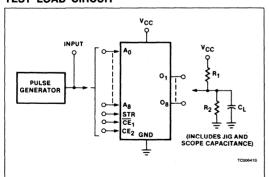

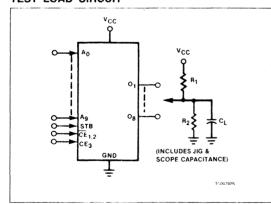

Fig. 4 load capacitance C<sub>L</sub>)

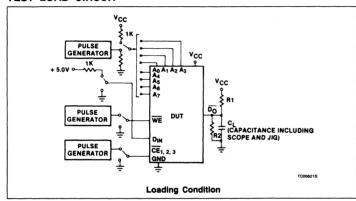

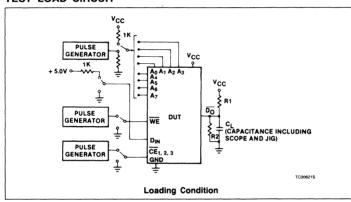

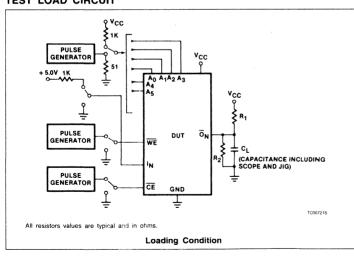

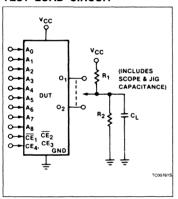

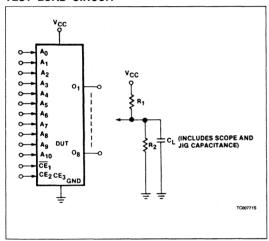

Fig. 4 Test load.

### A.C. CHARACTERISTICS (VDD = 5 V)

$V_{DD}$  = 5 ± 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to +70 °C; loads as per Fig. 4 with  $C_L$  = 100 pF unless otherwise specified

| parameter                                                 | symbol           | min. | typ.     | max. | unit |

|-----------------------------------------------------------|------------------|------|----------|------|------|

| Read cycle                                                |                  |      |          |      |      |

| Read cycle time                                           | <sup>t</sup> RC  | 150  | _        | _    | ns   |

| Address access time                                       | <sup>t</sup> AA  |      | _        | 150  | ns   |

| Chip enable CE1 to output                                 | tCO1             | _    | - ,      | 150  | ns   |

| Chip enable CE2 to output                                 | tCO2             |      | <u>-</u> | 150  | ns   |

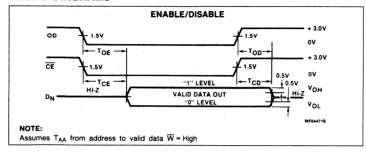

| Output disable OD to output                               | tOD              | _    | _        | 70   | ns   |

| Data output to high impedance state at $C_L = 5 pF$       | <sup>t</sup> DF  | 10   | _        | 70   | ns   |

| Previously read data valid with respect to address change | t <sub>OH1</sub> | 10   | _        | _    | ns   |

| Previously read data valid with respect to chip enable    | tOH2             | 10   | _        | _    | ns   |

| Write cycle                                               |                  |      |          |      |      |

| Write cycle time                                          | tWC              | 150  | _        | -    | ns   |

| Write delay time                                          | tAW              | 0    | _        | -    | ns   |

| Chip enable CE1 to write                                  | tCW1             | 120  | -        | -    | ns   |

| Chip enable CE2 to write                                  | tCW2             | 120  | -        | -    | ns   |

| Data set-up time                                          | t <sub>DW</sub>  | 70   | _        | -    | ns   |

| Data hold time                                            | <sup>t</sup> DH  | 0    | _        | -    | ns   |

| Write pulse duration                                      | tWP              | 70   | -        | -    | ns   |

| Write recovery time                                       | twR              | 0    | _        | -    | ns   |

| Output disable OD set-up time                             | tDS              | 70   | _        | -    | ns   |

### A.C. TEST CONDITIONS (V<sub>DD</sub> = 3 V)

Input pulse levels 0,4 V to 1,6 V

Input rise and fall times 5 ns

Input timing reference levels 1,0 V

Output timing levels 1,0 V

Output timing levels for high/low

impedance 0,7 V and 1,7 V  $\,$

Output load Fig. 5

Fig. 5 Test load.

### A.C. CHARACTERISTICS (V<sub>DD</sub> = 3 V)

$V_{DD}$  = 3 ± 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to +70 °C; loads as per Fig. 5 with  $C_L$  = 100 pF unless otherwise specified

| parameter                                                    | symbol           | min. | typ. | max.                                    | unit |

|--------------------------------------------------------------|------------------|------|------|-----------------------------------------|------|

| Read cycle                                                   |                  |      |      |                                         |      |

| Read cycle time                                              | tRC              | 400  | -    | -                                       | ns   |

| Address access time                                          | tAA              | _    | -    | 400                                     | ns   |

| Chip enable CE1 to output                                    | tCO1             | _    | -    | 400                                     | ns   |

| Chip enable CE2 to output                                    | tCO2             | _    | -    | 400                                     | ns   |

| Output disable OD to output                                  | tOD              | _    | -    | 200                                     | ns   |

| Data output to high impedance state at C <sub>L</sub> = 5 pF | t <sub>DF</sub>  | 10   | _    | 200                                     | ns   |

| Previously read data valid with respect to address change    | t <sub>OH1</sub> | 10   | _    | - 1 - 1 × 1 × 1 × 1 × 1 × 1 × 1 × 1 × 1 | ns   |

| Previously read data valid with respect to chip enable       | tOH2             | 10   | _    | -<br>-                                  | ns   |

| Write cycle                                                  |                  |      |      |                                         |      |

| Write cycle time                                             | twc              | 400  | _    | 1-                                      | ns   |

| Write delay time                                             | tAW              | 0    |      |                                         | ns   |

| Chip enable CE1 to write                                     | tCW1             | 300  | _    | _                                       | ns   |

| Chip enable CE2 to write                                     | tCW2             | 300  |      | <u>-</u> -                              | ns   |

| Data set-up time                                             | t <sub>DW</sub>  | 200  | _    | _                                       | ns   |

| Data hold time                                               | <sup>t</sup> DH  | 0    |      |                                         | ns   |

| Write pulse duration                                         | t <sub>WP</sub>  | 200  | -    |                                         | ns   |

| Write recovery time                                          | twR              | 0    | _    |                                         | ns   |

| Output disable OD set-up time                                | tDS              | 200  | -    | _                                       | ns   |

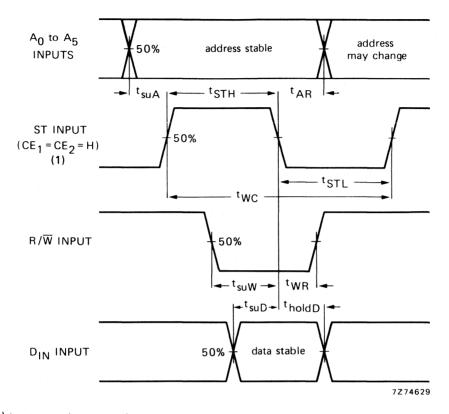

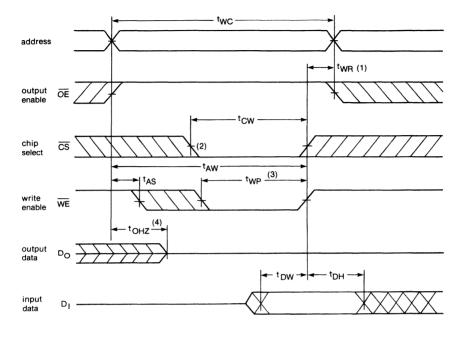

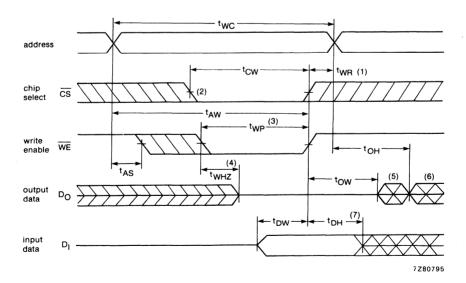

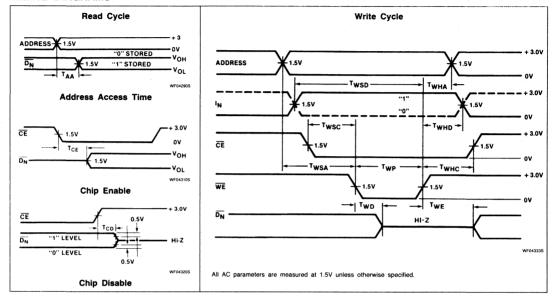

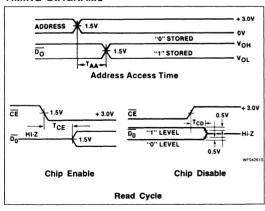

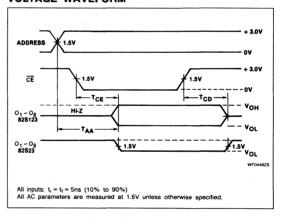

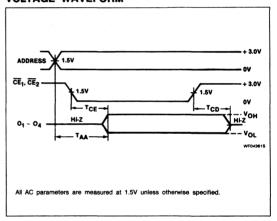

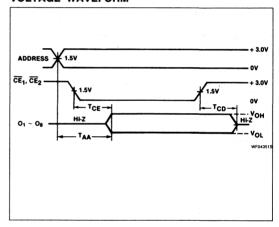

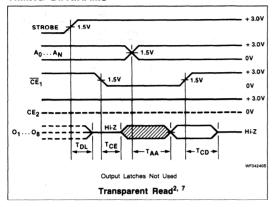

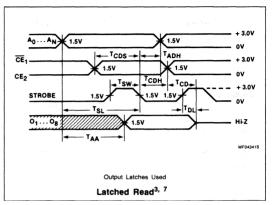

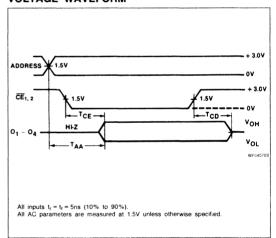

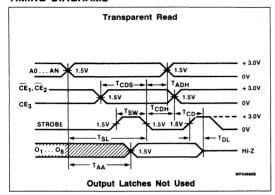

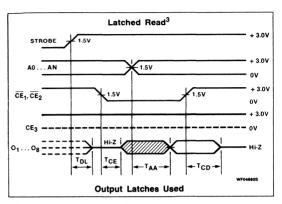

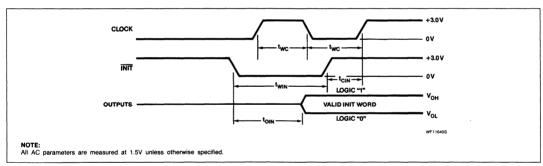

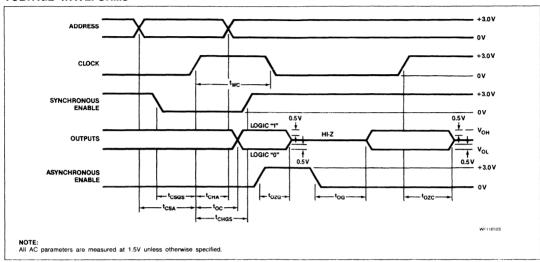

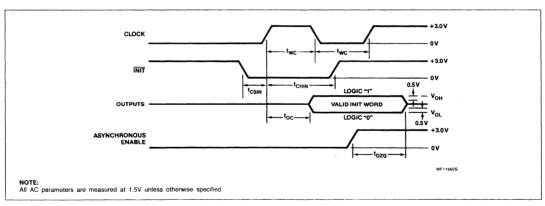

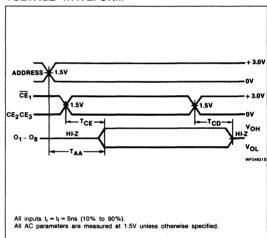

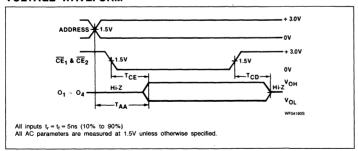

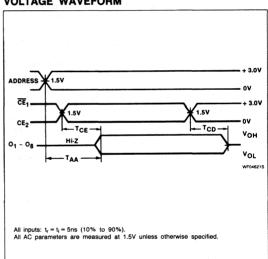

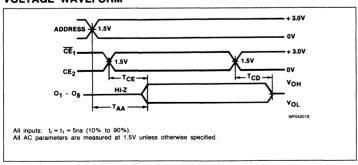

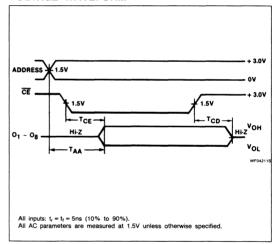

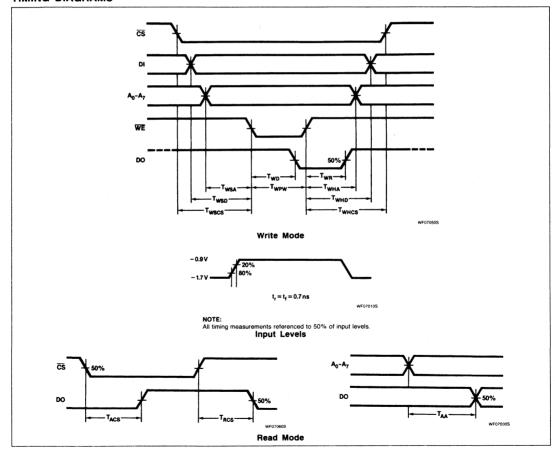

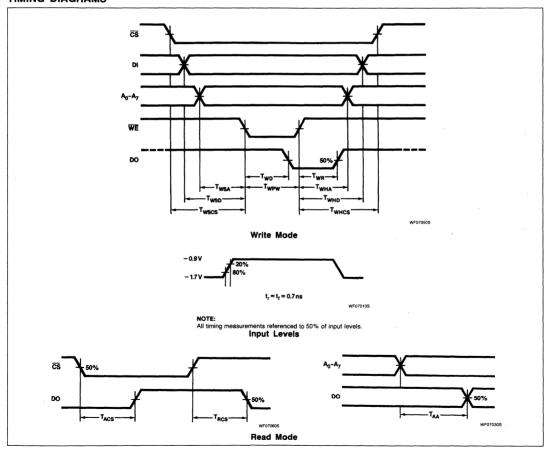

### **WAVEFORMS**

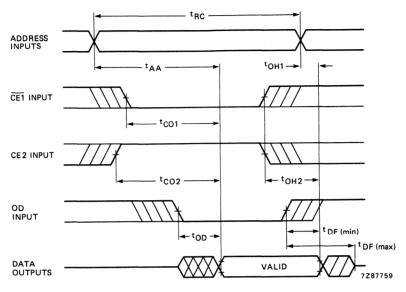

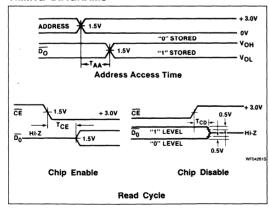

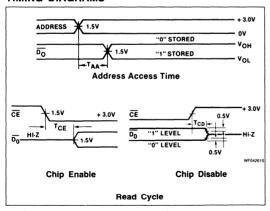

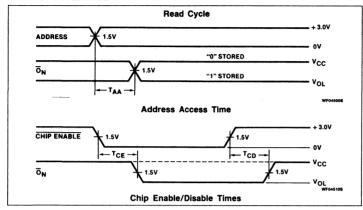

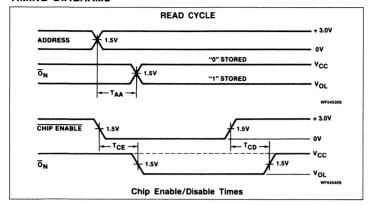

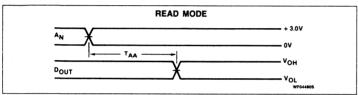

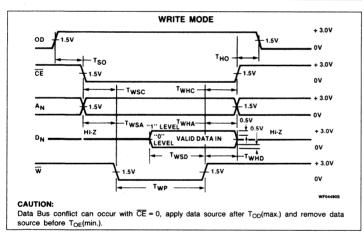

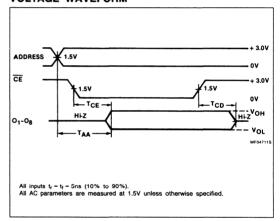

Fig. 6 Read cycle timing;  $R/\overline{W} = HIGH$ .

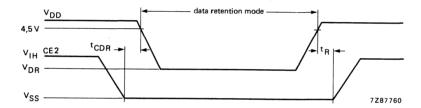

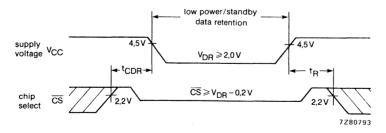

### LOW SUPPLY VOLTAGE DATA RETENTION CHARACTERISTICS

CE2  $\leq$  0,2 V;  $T_{amb} = -25 \text{ to } + 70 \text{ }^{\circ}\text{C}$ .

| parameter                                         | symbol | min.               | typ. | max. | unit |

|---------------------------------------------------|--------|--------------------|------|------|------|

| Supply voltage for data retention                 | VDR    | 1,0                | _    | 5,5  | V    |

| Data retention current at V <sub>DD</sub> = 1,5 V | IDR    | · · · <u>-</u> · · | 0,02 | 2,0  | μΑ   |

| Chip deselect to data retention time              | tCDR   | 0                  | _    |      | ns   |

| Operation recovery time                           | tR     | 0                  | _    |      | ns   |

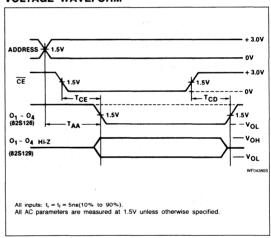

Fig. 8 Low supply voltage data retention characteristics.

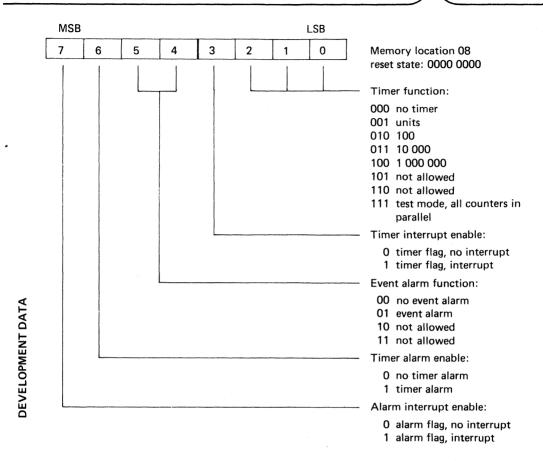

# **DEVELOPMENT DATA**

This data sheet contains advance information and specifications are subject to change without notice.

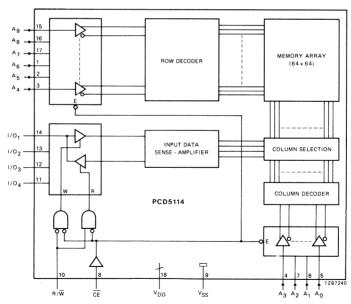

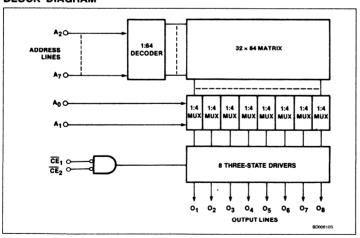

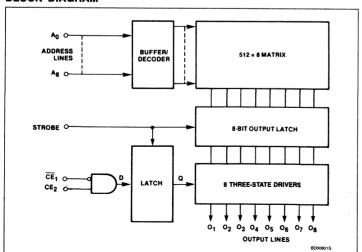

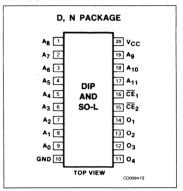

## 1024 x 4-BIT STATIC RAM

## GENERAL DESCRIPTION

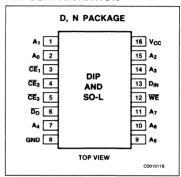

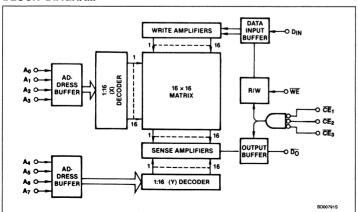

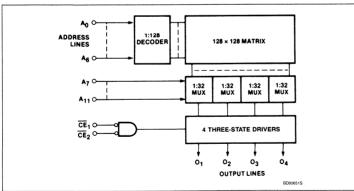

The PCD5114 is a low-power, high-speed 4096-bit static CMOS RAM, organized as 1024 words of 4 bits each. The IC is suitable for low power and high speed applications, for battery operation and where battery backup is required. Inputs R/W and CE control the read/write operation and standby mode respectively. The PCD5114 is pin compatible with the SBB2114 types.

#### **Features**

Operating supply voltage

· Low data retention voltage

Low standby current

Cycle time = access time

• Static operation requiring no clock or timing strobe

• Low power consumption

3-state common data input/output interface

All inputs and outputs directly TTL compatible

• Pin compatible with SBB2114 variants

• 18-lead DIL package

• 20-lead SO package

2,5 V to 5,5 V min. 1,0 V max. 5  $\mu$ A max. 200 ns

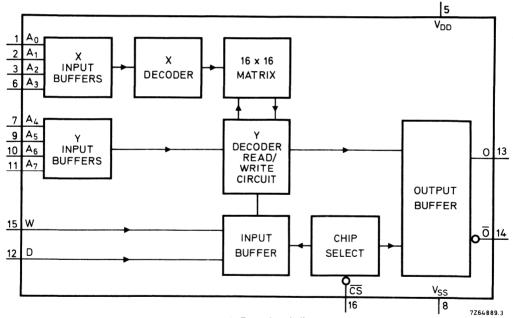

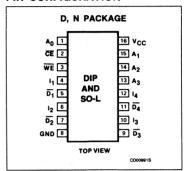

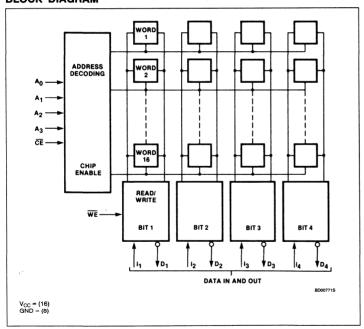

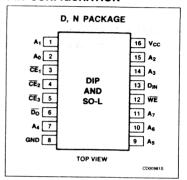

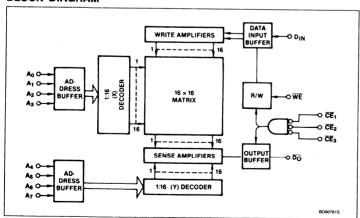

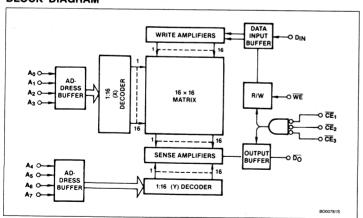

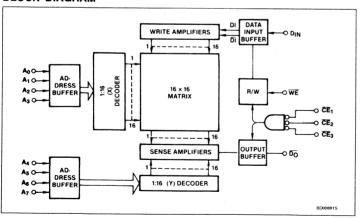

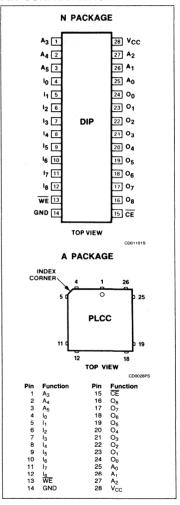

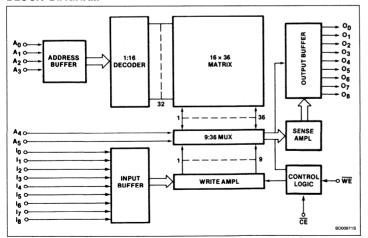

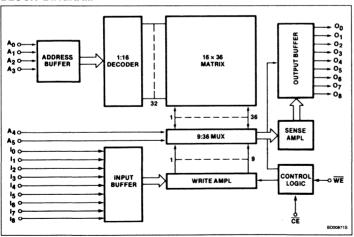

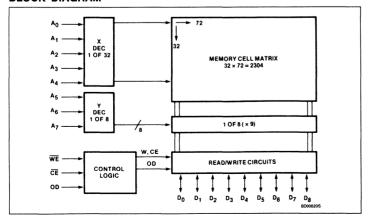

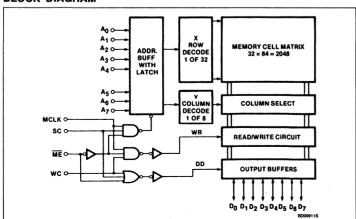

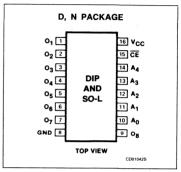

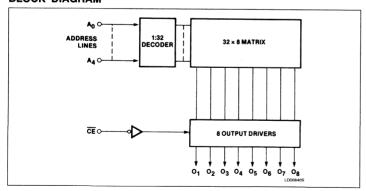

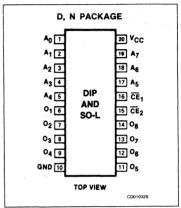

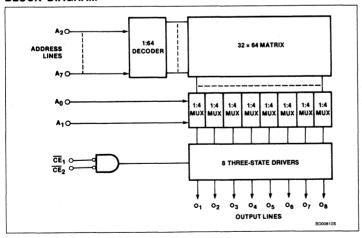

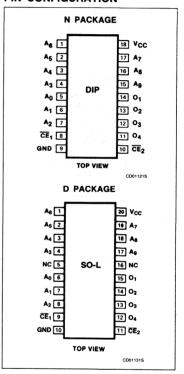

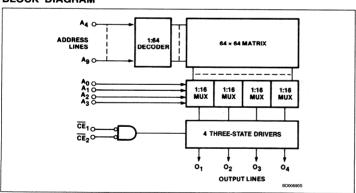

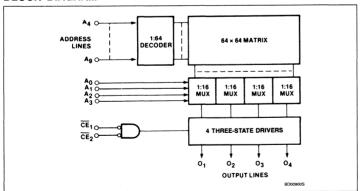

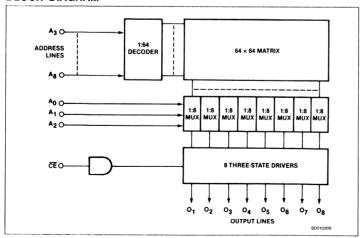

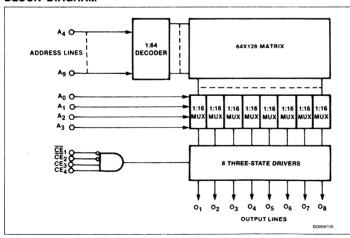

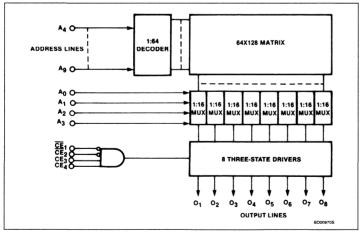

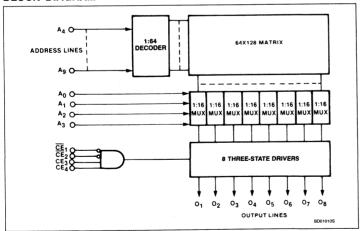

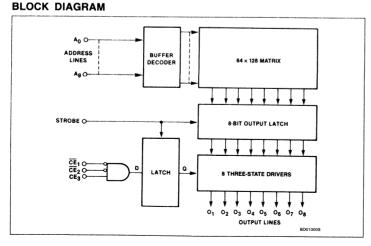

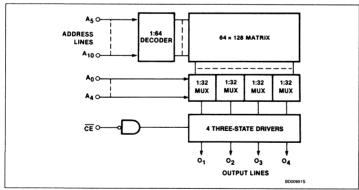

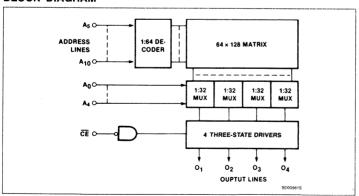

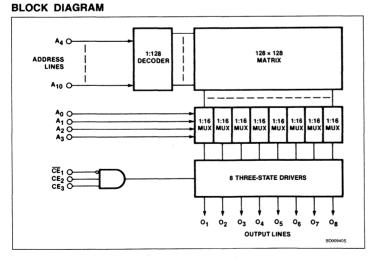

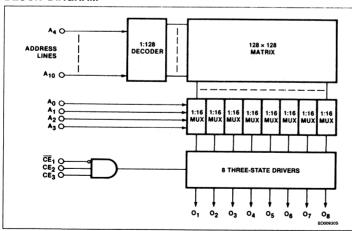

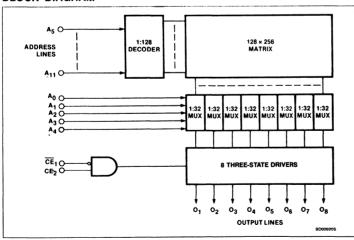

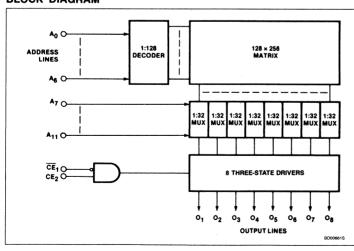

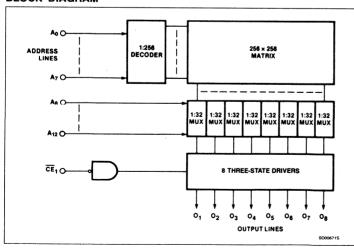

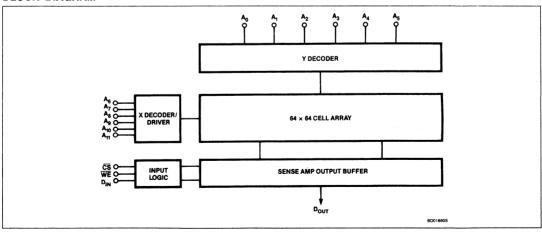

Fig. 1 Block diagram.

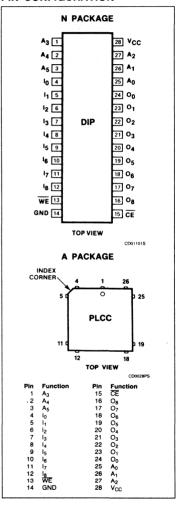

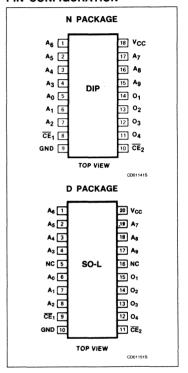

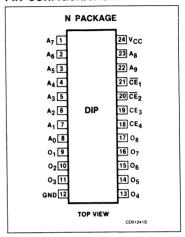

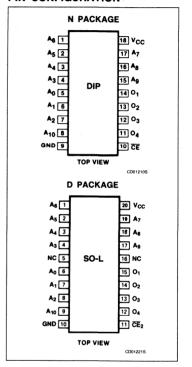

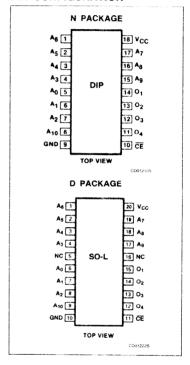

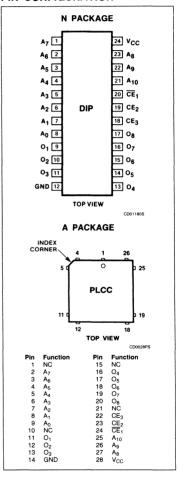

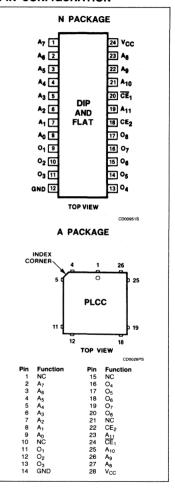

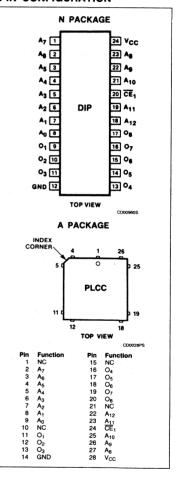

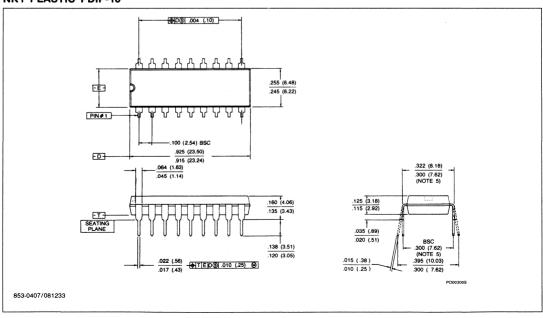

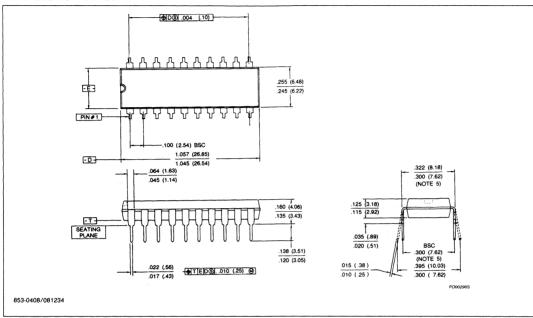

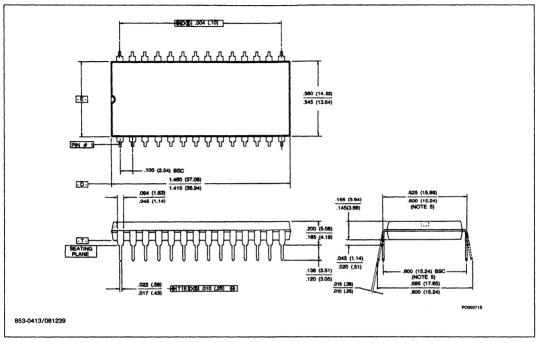

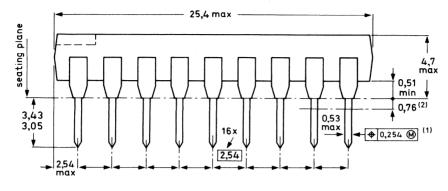

## **PACKAGE OUTLINES**

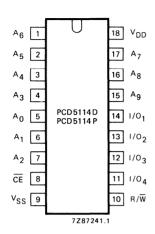

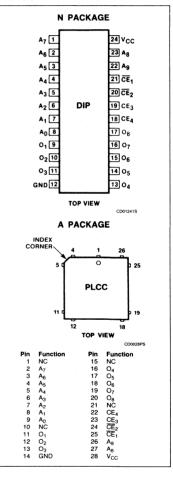

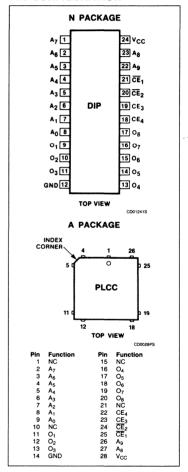

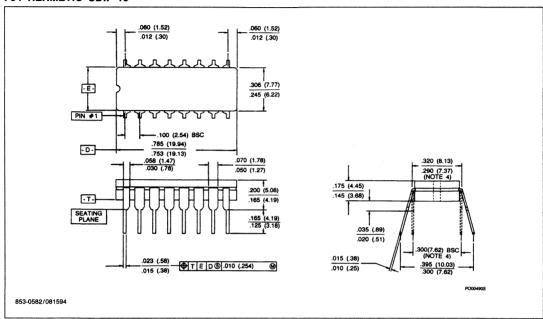

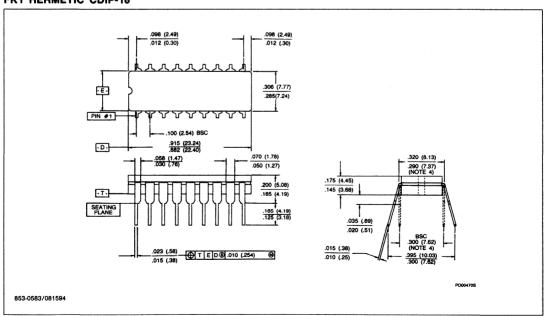

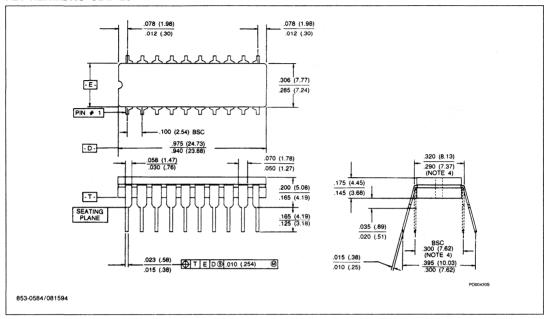

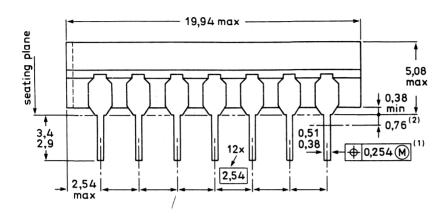

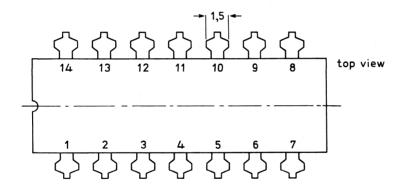

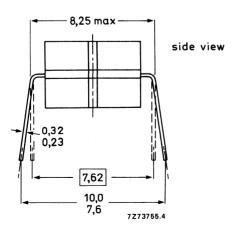

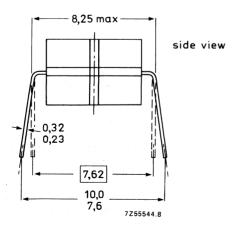

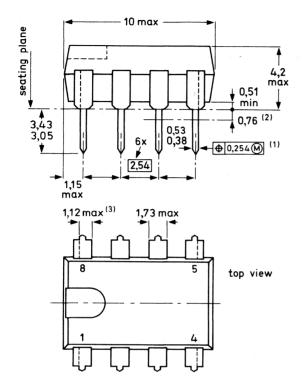

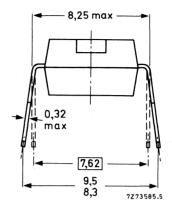

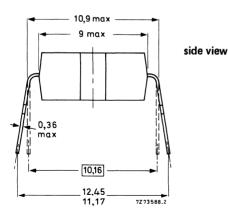

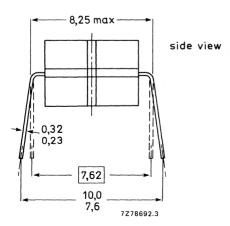

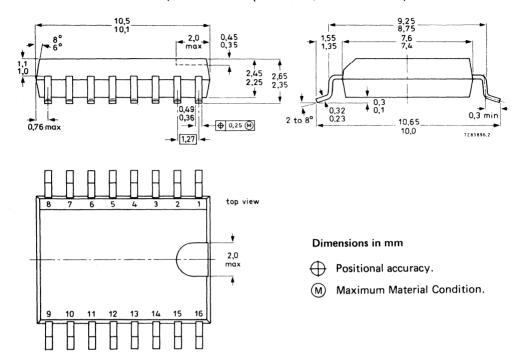

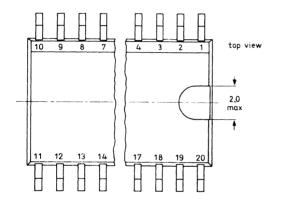

PCD5114D: 18-lead DIL; ceramic (cerdip) (SOT-133B).

PCD5114P: 18-lead DIL; plastic (SOT-102GE).

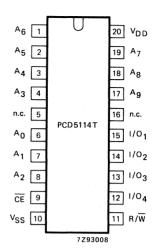

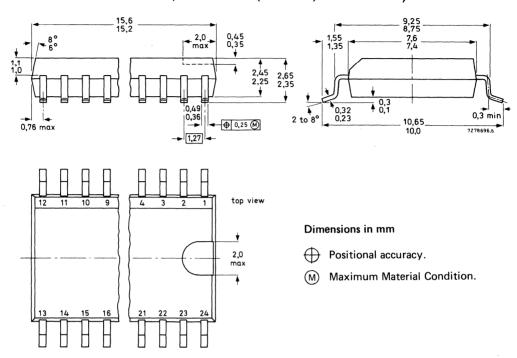

PCD5114T: 20-lead mini-pack; plastic (SO-20; SOT-163A).

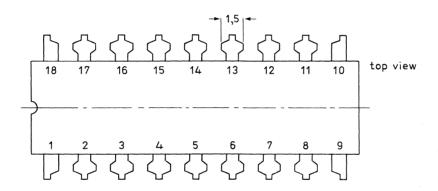

Fig. 2 Pinning diagram: PCD5114D; PCD5114P.

Fig. 3 Pinning diagram: PCD5114T.

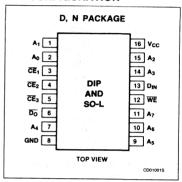

| An to Ag         | column address inputs |

|------------------|-----------------------|

| A4 to A9         | row address inputs    |

| CE               | chip enable input     |

| $R/\overline{W}$ | read/write input      |

I/O<sub>1</sub> to I/O<sub>4</sub> data input/outputVSS negative supply (ground)VDD positive supply (+ 5 V)

Table 1 Mode selection

| CE          | R/W              | mode                                          | output                                                       | power                                  |

|-------------|------------------|-----------------------------------------------|--------------------------------------------------------------|----------------------------------------|

| H<br>H<br>L | H<br>L<br>H<br>L | not selected<br>not selected<br>read<br>write | high impedance<br>high impedance<br>active<br>high impedance | standby<br>standby<br>active<br>active |

H = HIGH logic level (the most positive voltage)

L = LOW logic level (the most negative voltage)

## **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Supply voltage range  $V_{DD}$  -0.3 to + 8 V Input voltage range (any pin)  $V_{I}$   $V_{SS}-0.3 \text{ to } V_{DD}+0.3 \text{ V}$  Storage temperature range  $T_{stg}$  -55 to + 125 oC Operating ambient temperature range  $T_{amb}$  -25 to + 70 oC

## **HANDLING**

Inputs and outputs are protected against electrostatic charge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see "Handling MOS Devices").

## D.C. CHARACTERISTICS

$V_{DD}$  = 5 V  $\pm$  0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to + 70 °C; unless otherwise specified

| parameter                                                                                                                                                                                                                 | symbol            | min.        | typ.           | max.           | unit           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|----------------|----------------|----------------|

| Operating supply current at V <sub>I</sub> = V <sub>DD</sub> /V <sub>SS</sub> ; f = 1 MHz; outputs open at V <sub>I</sub> = 0,8 V/2,0 V; f = 1 MHz; outputs open at V <sub>I</sub> = 0,8 V/2,0 V; f = 5 MHz; outputs open | IDD<br>IDD        |             | 10<br>10<br>12 | 17<br>17<br>20 | mA<br>mA<br>mA |

| Standby current at CE = V <sub>DD</sub> Input voltage HIGH                                                                                                                                                                | I <sub>SB</sub>   | -           | 0,02           | 5              | μA<br>V        |

| Input voltage LOW                                                                                                                                                                                                         | VIH               | 2,0<br>-0,3 |                | +0,8           | V              |

| Input leakage current at V <sub>I</sub> = V <sub>SS</sub> to V <sub>DD</sub>                                                                                                                                              | ± IIL             |             | <u>.</u> .     | 0,1            | μΑ             |

| Output voltage HIGH at -I <sub>OH</sub> = 2 mA Output voltage LOW                                                                                                                                                         | Vон               | 2,4         | _              | <del>-</del> 2 | V              |

| at IOL = 4 mA  Output leakage current                                                                                                                                                                                     | VOL               |             | _              | 0,4            | V              |

| at V <sub>O</sub> = V <sub>SS</sub> to V <sub>DD</sub> ; $\overline{\text{CE}}$ = HIGH                                                                                                                                    | <sup>± I</sup> OL | _           | <del>-</del>   | 0,5            | μΑ             |

## D.C. CHARACTERISTICS

$V_{DD}$  = 3 V ± 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to + 70 °C; unless otherwise specified

| parameter                                                                                                                                                          | symbol     | min.           | typ.     | max.                  | unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|----------|-----------------------|----------|

| Operating supply current  at V <sub>I</sub> = V <sub>DD</sub> /V <sub>SS</sub> ; f = 1 MHz; outputs open  at V <sub>I</sub> = 0,4 V/1,6 V; f = 1 MHz; outputs open | lDD<br>lDD |                | 5<br>5   | 8<br>8                | mA<br>mA |

| Standby current at CE = V <sub>DD</sub>                                                                                                                            | ISB        | _              | 0,02     | 5                     | μΑ       |

| Input voltage HIGH                                                                                                                                                 | VIH        | 1,6            | _        | V <sub>DD</sub> + 0,3 | V        |

| Input voltage LOW                                                                                                                                                  | VIL        | -0,3           | _        | +0,4                  | V        |

| Input leakage current<br>at V <sub>I</sub> = V <sub>SS</sub> to V <sub>DD</sub>                                                                                    | ± 11L      | _              | _        | 0,1                   | μΑ       |

| Output voltage HIGH<br>at -I <sub>OH</sub> = 1 mA                                                                                                                  | Voн        | 1,7            |          | _                     | V        |

| Output voltage LOW at IOL = 1 mA                                                                                                                                   | VOL        | <sub>2</sub> — |          | 0,3                   | V        |

| Output leakage current at $V_0 = V_{SS}$ to $V_{DD}$ ; $\overline{CE} = HIGH$                                                                                      | ± IOL      | _              | <u>-</u> | 0,5                   | μΑ       |

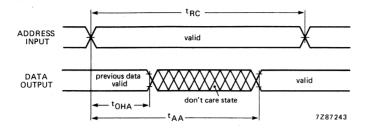

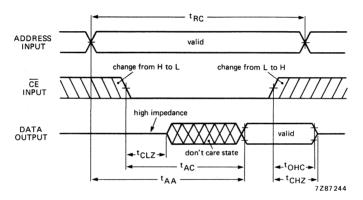

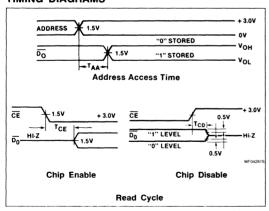

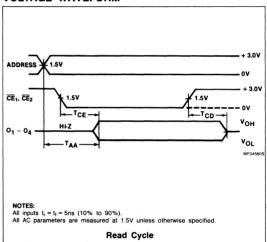

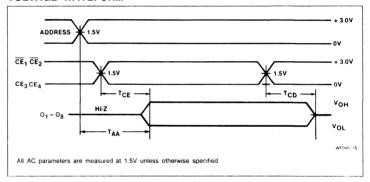

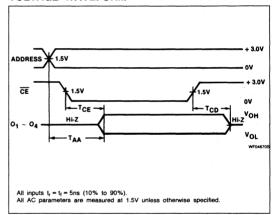

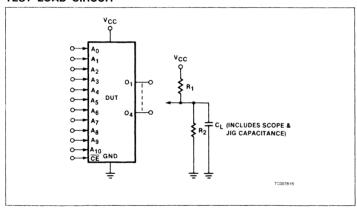

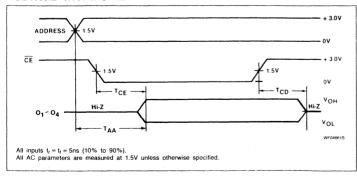

## A.C. CHARACTERISTICS

$V_{DD}$  = 5 V  $\pm$ 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to + 70 °C; measured in Fig. 4,  $C_L$  = 100 pF; unless otherwise specified

| parameter                                                      | symbol           | min. | typ. | max. | unit |

|----------------------------------------------------------------|------------------|------|------|------|------|

| Read cycle                                                     |                  |      |      |      |      |

| Read cycle time                                                | tRC              | 200  |      |      | ns   |

| Address access time                                            | tAA              | _    | _    | 200  | ns   |

| Chip select access time                                        | tAC              | -    | _    | 200  | ns   |

| Output hold from address change                                | tOHA             | 20   | _    | _    | ns   |

| Output hold from chip select                                   | tOHC             | 20   |      | _    | ns   |

| Output to low impedance from chip selection at $C_L = 5 pF$    | <sup>t</sup> CLZ | 20   | _    |      | ns   |

| Output to high impedance from chip deselection at $C_L = 5 pF$ | <sup>†</sup> CHZ | _    | _    | 80   | ns   |

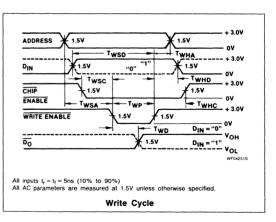

| Write cycle                                                    |                  |      |      |      |      |

| Write cycle time                                               | tWC              | 200  | _    | _    | ns   |

| Chip selection to end of write                                 | tCW              | 120  | _    | _    | ns   |

| Address set-up time                                            | tAS              | 0    | _    | _    | ns   |

| Write pulse duration                                           | twp              | 140  | _    |      | ns   |

| Write recovery time                                            | twR              | 0    | _    | _    | ns   |

| Data set-up time                                               | t <sub>DS</sub>  | 80   | _    | _    | ns   |

| Data hold time                                                 | tDH              | О    |      | _    | ns   |

| Output to high impedance from write enabled at $C_L = 5 pF$    | twz              | _    | _    | 60   | ns   |

| Output active from end of write at $C_L = 5 pF$                | tRZ              | 20   | _    | _    | ns   |

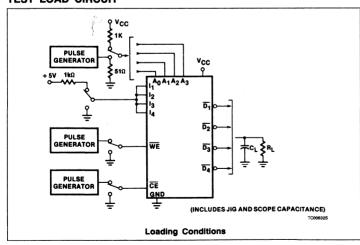

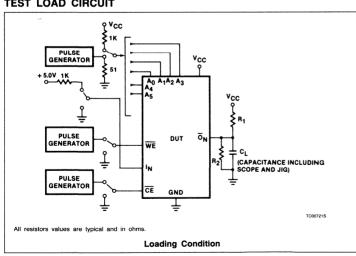

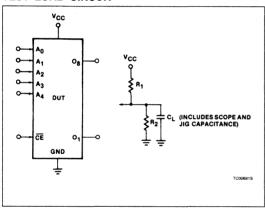

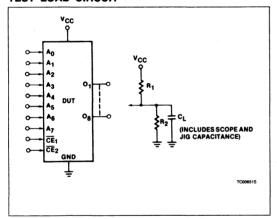

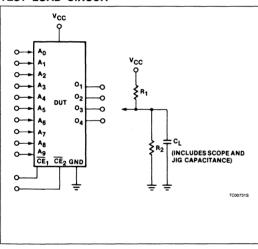

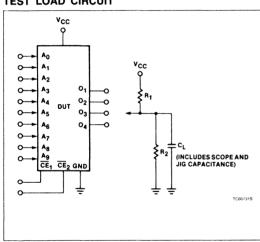

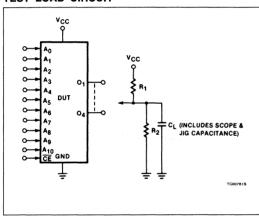

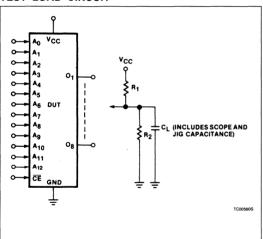

## A.C. TEST CONDITIONS (see Fig. 4)

Input pulse levels 0,8 V to 2,0 V Input rise and fall times 5 ns Input timing reference levels 1,5 V Output timing levels 1,5 V Output timing levels for high/low impedance 1,2 V and 2,8 V Output load 2 TTL gates and  $C_L = 100$  pF

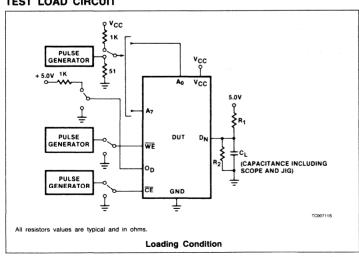

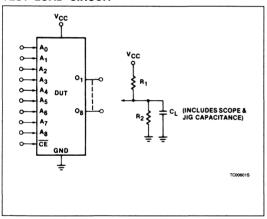

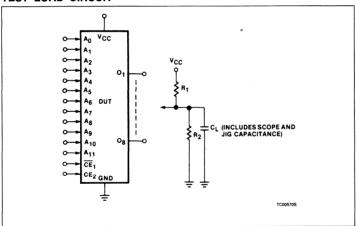

Fig. 4 Load for a.c. test conditions  $(V_{DD} = 5 V \pm 0.5 V)$ .

## A.C. CHARACTERISTICS

$V_{DD}$  = 3 V ± 0,5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 to + 70°C; measured in Fig. 5,  $C_L$  = 100 pF; unless otherwise specified

| parameter                                                      | symbol | min.   | typ.                                    | max.     | unit |

|----------------------------------------------------------------|--------|--------|-----------------------------------------|----------|------|

| Read cycle                                                     |        |        |                                         |          |      |

| Read cycle time                                                | tRC    | 500    | _                                       | _        | ns   |

| Address access time                                            | tAA    | _      |                                         | 500      | ns   |

| Chip select access time                                        | tAC    | _      | -                                       | 500      | ns   |

| Output hold from address change                                | tOHA   | 20     | _                                       | <u> </u> | ns   |

| Output hold from chip select                                   | tOHC   | 20     | _                                       |          | ns   |

| Output to low impedance from chip selection at $C_L = 5 pF$    | tCLZ   | 20     | _                                       | _        | ns   |

| Output to high impedance from chip deselection at $C_L = 5 pF$ | tCHZ   | _      | _                                       | 200      | ns   |

| Write cycle                                                    |        | 1      |                                         |          |      |

| Write cycle time                                               | tWC    | 500    | _                                       | _        | ns   |

| Chip selection to end of write                                 | tcw    | 300    | -                                       | _        | ns   |

| Adress set-up time                                             | tAS    | 0      | _                                       | _        | ns   |

| Write pulse duration                                           | tWP    | 350    | _                                       | _        | ns   |

| Write recovery time                                            | twR    | 0      | _                                       | _        | ns   |

| Data set-up time                                               | tDS    | 200    | -                                       |          | ns   |

| Data hold time                                                 | tDH    | 0      | _                                       | _        | ns   |

| Output to high impedance from write enabled at $C_L = 5 pF$    | twz    | -<br>- |                                         | 150      | ns   |

| Output active from end of write at $C_L = 5 pF$                | tRZ    | 20     | 12 - 12 - 12 - 12 - 12 - 12 - 12 - 12 - | _        | ns   |

## A.C. TEST CONDITIONS (see Fig. 5)

Input pulse levels 0,4 V to 1,6 V Input rise and fall times 5 ns Input timing reference levels 1,0 V Output timing levels 1,0 V Output timing levels for high/low impedance 0,7 V and 1,7 V Output load 2 TTL gates and  $C_L = 100 \ pF$

Fig. 5 Load for a.c. test conditions  $(V_{DD} = 3 V \pm 0.5 V)$ .

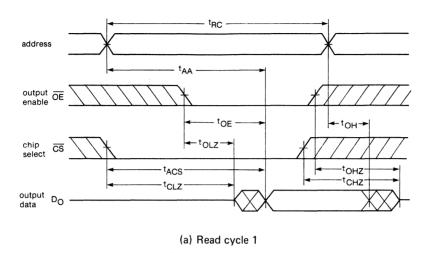

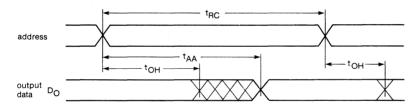

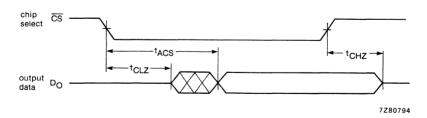

Fig. 6 Read cycle timing (1): R/W is HIGH; CE is LOW for a read cycle.

Fig. 7 Read cycle timing (2): R/W is HIGH for a read cycle.

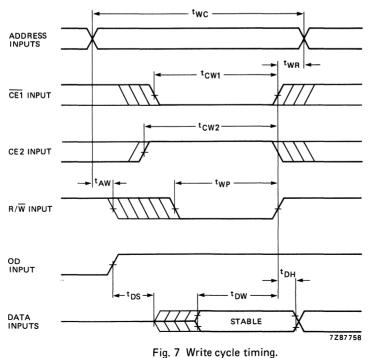

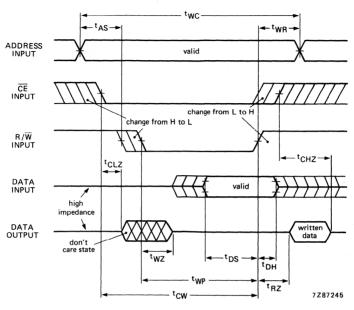

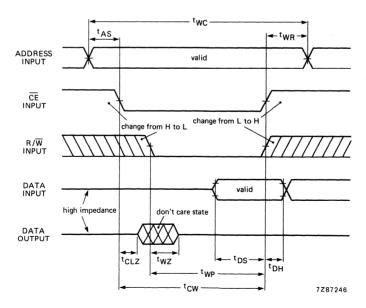

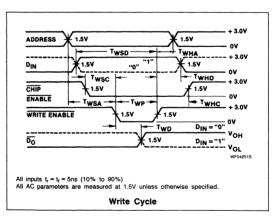

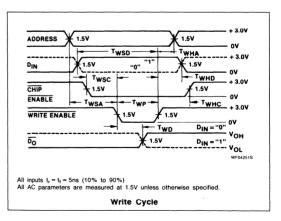

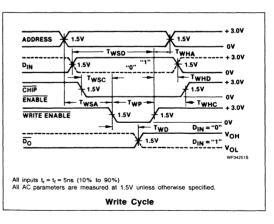

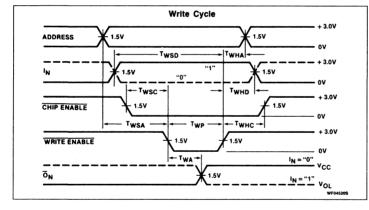

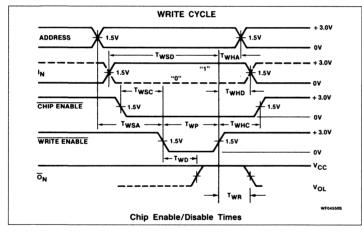

Fig. 8 Write cycle (1):  $R/\overline{W}$  controlled.

Fig. 9 Write cycle (2):  $\overline{\text{CE}}$  controlled.

Note: If the  $\overline{CE}$  low transition occurs after the R/ $\overline{W}$  low transition, the outputs remain in the high impedance state.

## **CAPACITANCE**

$f = 1 MHz; T_{amb} = 25 °C$

| parameter                                                 | symbol         | min. | typ. | max. | unit |

|-----------------------------------------------------------|----------------|------|------|------|------|

| Input capacitance at V <sub>I</sub> = V <sub>SS</sub>     | CI             | _    |      | 5    | рF   |

| Output capacitance<br>at V <sub>O</sub> = V <sub>SS</sub> | c <sub>O</sub> |      | _    | 5    | рF   |

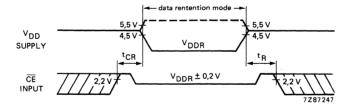

# LOW V<sub>DD</sub> DATA RETENTION CHARACTERISTICS

$T_{amb} = -25 \text{ to } + 70 \text{ }^{\circ}\text{C}$

| parameter                                                                                                                                        | symbol           | min. | typ. | max. | unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|------|

| V <sub>DD</sub> for data retention<br>at $\overline{\text{CE}}$ = V <sub>DDR</sub> ± 0,2 V; V <sub>I</sub> = V <sub>DDR</sub> to V <sub>SS</sub> | V <sub>DDR</sub> | 1    | _    | 5,5  | V    |

| Data retention current at V <sub>DDR</sub> = 1,5 V                                                                                               | IDDR             | _    | 0,02 | 2    | μΑ   |

| Chip deselect to data retention time                                                                                                             | <sup>t</sup> CR  | 0    | -    | -    | ns   |

| Operation recovery time                                                                                                                          | <sup>t</sup> R   | 0    | _    | _    | ns   |

Fig. 10 LOW V<sub>DD</sub> data retention.

This data sheet contains advance information and specifications are subject to change without notice.

## 256 x 8-BIT STATIC RAM

## GENERAL DESCRIPTION

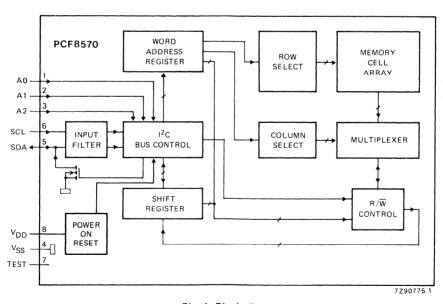

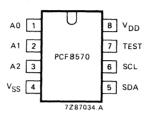

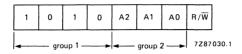

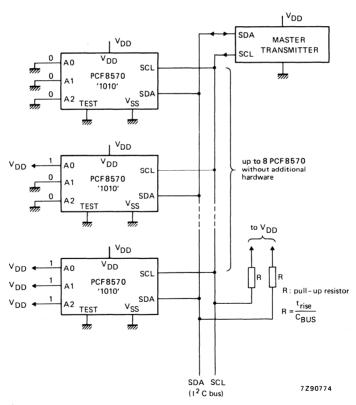

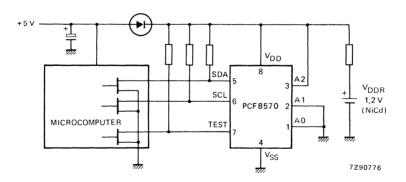

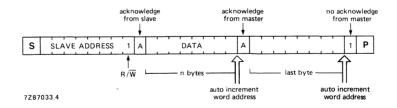

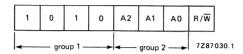

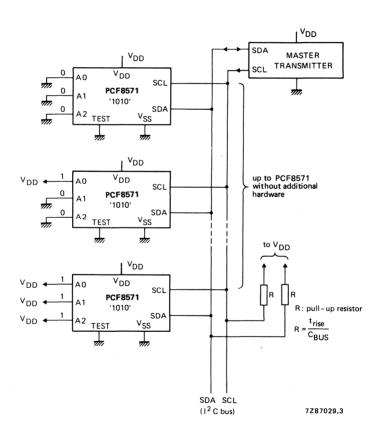

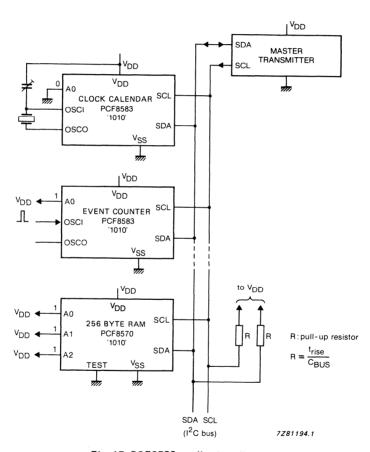

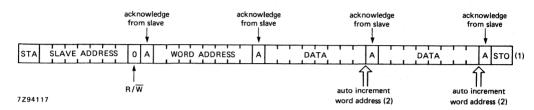

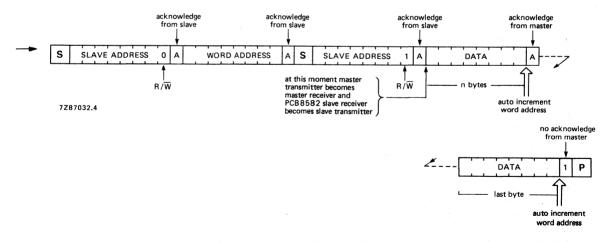

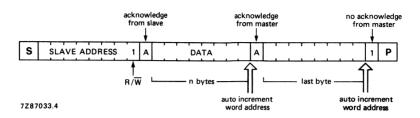

The PCF8570 is a low power 2048-bit static CMOS RAM organized as 256 words by 8-bits. Addresses and data are transferred serially via a two-line bidirectional bus (I2C). The built-in word address register is incremented automatically after each written or read data byte. Three address pins A0, A1, A2 are used for programming the hardware address, allowing the use of up to eight devices connected to the bus without additional hardware.

#### **Features**

Operating supply voltage Low data retention voltage

Low standby current

Power saving mode

2.5 V to 6 V min, 1,0 V max.  $15 \mu A$

typ. 50 nA

Serial input/output bus (I<sup>2</sup>C)

Address by 3 hardware address pins

Automatic word address incrementing

• 8-lead DIL package

## **Applications**

Telephony

Radio and television Video cassette recorder

General purpose

RAM expansion for stored numbers in repertory dialling

(e.g. PCD3343 applications)

channel presets

RAM expansion for the microcontroller families MAB8400 and PCF84C00

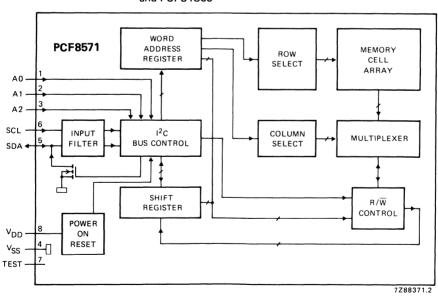

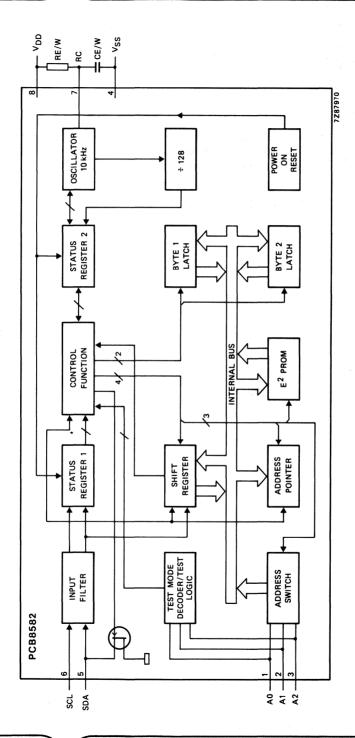

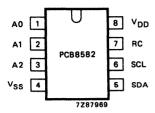

Fig. 1 Block diagram.

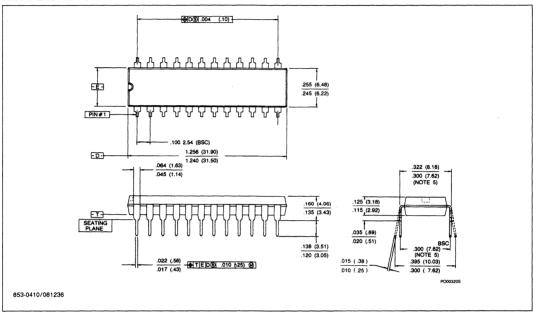

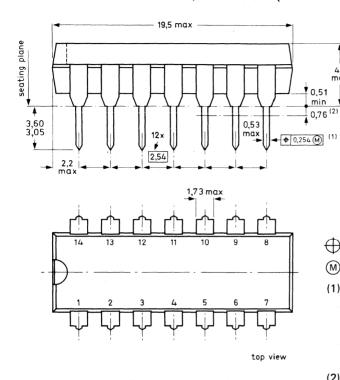

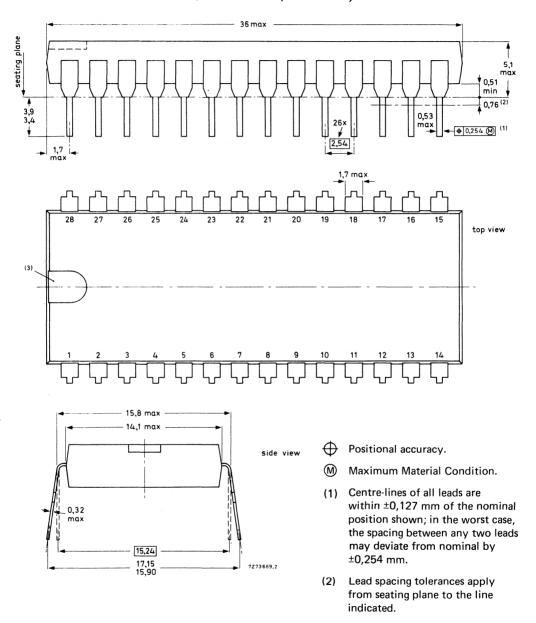

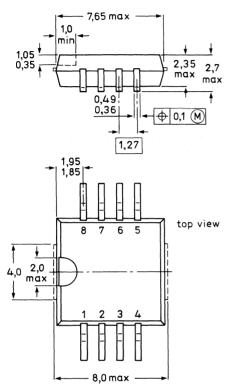

## PACKAGE OUTLINES

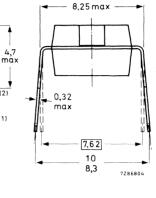

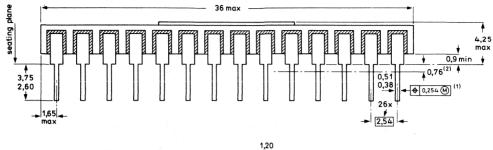

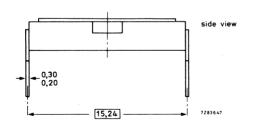

PCF8570P: 8-lead DIL; plastic (SOT-97AE).

PCF8570T: 8-lead mini-pack plastic (SO-8L; SOT-176).

## **PINNING**

| 1 to 3 | A0 to A2 | address inputs                                                                                                             |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 4      | $V_{SS}$ | negative supply                                                                                                            |

| 5      | SDA      | serial data line 120 bus                                                                                                   |

| 6      | SCL      | serial data line la                                                                    |

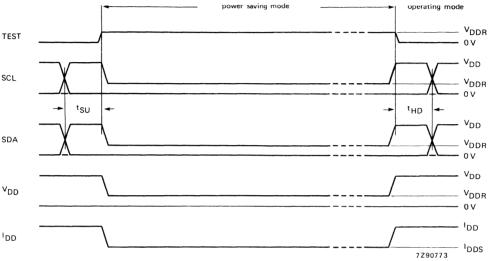

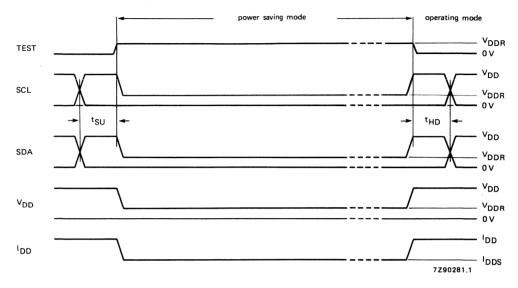

| 7      | TEST     | test input for test speed-up; must be connected to V <sub>SS</sub> when not in use (power saving mode, see Figs 14 and 15) |

| 8      | $V_{DD}$ | positive supply                                                                                                            |

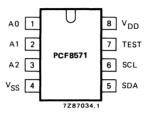

Fig. 2 Pinning diagram.

# **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage range (pin 8)        | $v_{DD}$                | -0,8      | 3 to + 8,0 V          |

|-------------------------------------|-------------------------|-----------|-----------------------|

| Voltage range on any input          | $v_I$                   | −0,8 to V | <sub>DD</sub> + 0,8 V |

| D.C. input current (any input)      | ±1                      | max.      | 10 mA                 |

| D.C. output current (any output)    | ± IO                    | max.      | 10 mA                 |

| Supply current (pin 4 or pin 8)     | ± I <sub>DD</sub> ; Iss | max.      | 50 mA                 |

| Power dissipation per package       | $P_{tot}$               | max.      | 300 mW                |

| Power dissipation per output        | P                       | max.      | 50 mW                 |

| Storage temperature range           | $T_{stg}$               | -65       | to + 150 °C           |

| Operating ambient temperature range | T <sub>amb</sub>        | -4        | 0 to + 85 °C          |

## **CHARACTERISTICS**

$V_{DD}$  = 2,5 to 6 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to + 85 °C unless otherwise specified

| parameter                                                   | symbol           | min.                  | typ. | max.                  | unit |

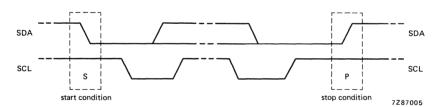

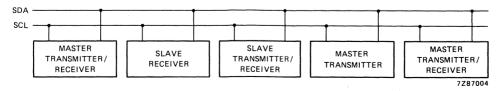

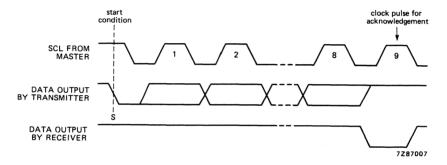

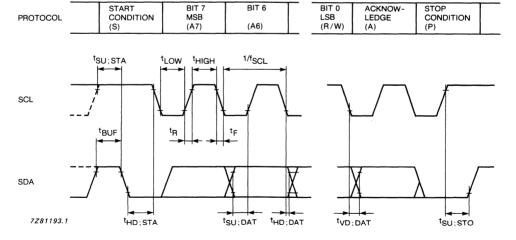

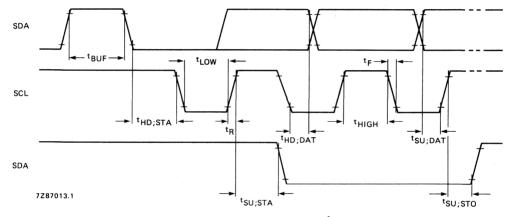

|-------------------------------------------------------------|------------------|-----------------------|------|-----------------------|------|